XC2VP30-6FGG676C Xilinx Inc, XC2VP30-6FGG676C Datasheet - Page 51

XC2VP30-6FGG676C

Manufacturer Part Number

XC2VP30-6FGG676C

Description

IC FPGA VIRTEX-II PRO 676-FBGA

Manufacturer

Xilinx Inc

Series

Virtex™-II Pror

Datasheet

1.XC2VP20-5FGG676C.pdf

(430 pages)

Specifications of XC2VP30-6FGG676C

Number Of Logic Elements/cells

30816

Number Of Labs/clbs

3424

Total Ram Bits

2506752

Number Of I /o

416

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

676-BBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Gates

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

XC2VP30-6FGG676C

Manufacturer:

XILINX

Quantity:

490

Part Number:

XC2VP30-6FGG676C

Manufacturer:

XILINX/赛灵思

Quantity:

20 000

- Current page: 51 of 430

- Download datasheet (4Mb)

Multiplexers

Virtex-II Pro function generators and associated multiplex-

ers can implement the following:

•

•

•

•

Fast Lookahead Carry Logic

Dedicated carry logic provides fast arithmetic addition and

subtraction. The Virtex-II Pro CLB has two separate carry

chains, as shown in the

The height of the carry chains is two bits per slice. The carry

chain in the Virtex-II Pro device is running upward. The ded-

icated carry path and carry multiplexer (MUXCY) can also

DS083 (v4.7) November 5, 2007

Product Specification

4:1 multiplexer in one slice

8:1 multiplexer in two slices

16:1 multiplexer in one CLB element (4 slices)

32:1 multiplexer in two CLB elements (8 slices)

R

G

G

F

F

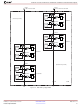

Figure

42.

Slice S3

Slice S2

Figure 41: MUXF5 and MUXFX multiplexers

Virtex-II Pro and Virtex-II Pro X Platform FPGAs: Functional Description

Slice S1

Slice S0

www.xilinx.com

G

G

F

F

Each Virtex-II Pro slice has one MUXF5 multiplexer and

one MUXFX multiplexer. The MUXFX multiplexer imple-

ments the MUXF6, MUXF7, or MUXF8, as shown in

Figure

one MUXF7 multiplexer and one MUXF8 multiplexer. Exam-

ples of multiplexers are shown in the Virtex-II Pro Platform

FPGA User Guide. Any LUT can implement a 2:1 multi-

plexer.

be used to cascade function generators for implementing

wide logic functions.

Arithmetic Logic

The arithmetic logic includes an XOR gate that allows a

2-bit full adder to be implemented within a slice. In addition,

a dedicated AND (MULT_AND) gate (shown in

improves the efficiency of multiplier implementation.

CLB

41. Each CLB element has two MUXF6 multiplexers,

MUXF8 combines

the two MUXF7 outputs

(Two CLBs)

MUXF6 combines the two MUXF5

outputs from slices S2 and S3

MUXF7 combines the two MUXF6

outputs from slices S0 and S2

MUXF6 combines the two MUXF6

outputs from slices S0 and S1

DS031_08_110200

Module 2 of 4

Figure

34)

40

Related parts for XC2VP30-6FGG676C

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC VIRTEXIIPRO FPGA 30K 676FCBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

IC FPGA VIRTEX-II PRO 896-FBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

IC FPGA VIRTEX-II PRO 1152-FBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

IC FPGA VIRTEX-II PRO 676-FBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

IC VIRTEXIIPRO FPGA 30K 896FCBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

IC FPGA VIRTEX-II PRO 896-FBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

IC FPGA VIRTEX-II PRO 1152-FBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

IC FPGA VIRTEX-II PRO 676-FBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

IC FPGA VIRTEX-II PRO 676-FBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

IC FPGA VIRTEX-II PRO 896-FBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

IC FPGA VIRTEX-II PRO 896-FBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

IC FPGA VIRTEX-II PRO 1152-FBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

IC FPGA VIRTEX-II PRO 1152-FBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

IC FPGA VIRTEX-II PRO 676FGBGA

Manufacturer:

Xilinx Inc

Datasheet:

Part Number:

Description:

IC FPGA VIRTEX-II PRO 896FFBGA

Manufacturer:

Xilinx Inc

Datasheet: