EP2S180F1508C4 Altera, EP2S180F1508C4 Datasheet - Page 14

EP2S180F1508C4

Manufacturer Part Number

EP2S180F1508C4

Description

IC STRATIX II FPGA 180K 1508FBGA

Manufacturer

Altera

Series

Stratix® IIr

Datasheet

1.EP2S15F484I4N.pdf

(238 pages)

Specifications of EP2S180F1508C4

Number Of Logic Elements/cells

179400

Number Of Labs/clbs

8970

Total Ram Bits

9383040

Number Of I /o

1170

Voltage - Supply

1.15 V ~ 1.25 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

1508-FBGA

For Use With

544-1701 - DSP PRO KIT W/SII EP2S180N

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Other names

544-1416

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

EP2S180F1508C4

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

Part Number:

EP2S180F1508C4ES

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

Company:

Part Number:

EP2S180F1508C4N

Manufacturer:

ALTERA

Quantity:

3 000

Part Number:

EP2S180F1508C4N

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

Adaptive Logic Modules

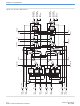

Figure 2–4. LAB-Wide Control Signals

Adaptive Logic

Modules

2–6

Stratix II Device Handbook, Volume 1

Dedicated Row LAB Clocks

Local Interconnect

Local Interconnect

Local Interconnect

Local Interconnect

Local Interconnect

Local Interconnect

6

6

signal with asynchronous load data input tied high. When the

asynchronous load/preset signal is used, the labclkena0 signal is no

longer available.

The LAB row clocks [5..0] and LAB local interconnect generate the

LAB-wide control signals. The MultiTrack

skew allows clock and control signal distribution in addition to data.

Figure 2–4

The basic building block of logic in the Stratix II architecture, the adaptive

logic module (ALM), provides advanced features with efficient logic

utilization. Each ALM contains a variety of look-up table (LUT)-based

resources that can be divided between two adaptive LUTs (ALUTs). With

up to eight inputs to the two ALUTs, one ALM can implement various

combinations of two functions. This adaptability allows the ALM to be

6

labclk0

clock signals per LAB.

There are two unique

shows the LAB control signal generation circuit.

or asyncload

or labpreset

labclkena0

labclk1

labclkena1

labclk2

labclkena2

TM

interconnect's inherent low

syncload

labclr0

Altera Corporation

labclr1

May 2007

synclr