EP2S180F1508C3 Altera, EP2S180F1508C3 Datasheet - Page 235

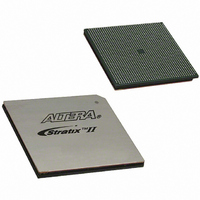

EP2S180F1508C3

Manufacturer Part Number

EP2S180F1508C3

Description

IC STRATIX II FPGA 180K 1508FBGA

Manufacturer

Altera

Series

Stratix® IIr

Datasheet

1.EP2S15F484I4N.pdf

(238 pages)

Specifications of EP2S180F1508C3

Number Of Logic Elements/cells

179400

Number Of Labs/clbs

8970

Total Ram Bits

9383040

Number Of I /o

1170

Voltage - Supply

1.15 V ~ 1.25 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

1508-FBGA

Family Name

Stratix II

Number Of Logic Blocks/elements

179400

# I/os (max)

1170

Frequency (max)

778.82MHz

Process Technology

90nm (CMOS)

Operating Supply Voltage (typ)

1.2V

Logic Cells

179400

Ram Bits

9383040

Operating Supply Voltage (min)

1.15V

Operating Supply Voltage (max)

1.25V

Operating Temp Range

0C to 85C

Operating Temperature Classification

Commercial

Mounting

Surface Mount

Pin Count

1508

Package Type

FC-FBGA

For Use With

544-1701 - DSP PRO KIT W/SII EP2S180N

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Lead Free Status / Rohs Status

Not Compliant

Other names

544-2164

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP2S180F1508C3

Manufacturer:

ALTERA

Quantity:

3 000

Company:

Part Number:

EP2S180F1508C3N

Manufacturer:

ALTERA

Quantity:

624

Part Number:

EP2S180F1508C3N

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

Altera Corporation

April 2011

January 2005,

v2.0

October 2004,

v1.2

July 2004, v1.1

February 2004,

v1.0

Table 5–103. Document Revision History (Part 3 of 3)

Document

Date and

Version

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

Added document to the Stratix II Device Handbook.

Updated the “Power Consumption” section.

Added the “High-Speed I/O Specifications” and

“On-Chip Termination Specifications” sections.

Removed the ESD Protection Specifications

section.

Updated Tables 5–3 through 5–13, 5–16 through

5–18, 5–21, 5–35, 5–39, and 5–40.

Updated tables in “Timing Model” section.

Added Tables 5–30 and 5–31.

Updated Table 5–3.

Updated introduction text in the “PLL Timing

Specifications” section.

Re-organized chapter.

Added typical values and C

Added undershoot specification to Note (4) for

Tables 5–1 through 5–9.

Added Note (1) to Tables 5–5 and 5–6.

Added V

Added “I/O Timing Measurement Methodology”

section.

Added Table 5–72.

Updated Tables 5–1 through 5–2 and Tables 5–24

through 5–29.

I D

and V

Changes Made

I C M

to Table 5–10.

O U T F B

to Table 5–32.

Stratix II Device Handbook, Volume 1

DC & Switching Characteristics

Summary of Changes

—

—

—

—

5–99