EP2S180F1508C3 Altera, EP2S180F1508C3 Datasheet - Page 122

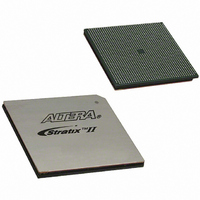

EP2S180F1508C3

Manufacturer Part Number

EP2S180F1508C3

Description

IC STRATIX II FPGA 180K 1508FBGA

Manufacturer

Altera

Series

Stratix® IIr

Datasheet

1.EP2S15F484I4N.pdf

(238 pages)

Specifications of EP2S180F1508C3

Number Of Logic Elements/cells

179400

Number Of Labs/clbs

8970

Total Ram Bits

9383040

Number Of I /o

1170

Voltage - Supply

1.15 V ~ 1.25 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

1508-FBGA

Family Name

Stratix II

Number Of Logic Blocks/elements

179400

# I/os (max)

1170

Frequency (max)

778.82MHz

Process Technology

90nm (CMOS)

Operating Supply Voltage (typ)

1.2V

Logic Cells

179400

Ram Bits

9383040

Operating Supply Voltage (min)

1.15V

Operating Supply Voltage (max)

1.25V

Operating Temp Range

0C to 85C

Operating Temperature Classification

Commercial

Mounting

Surface Mount

Pin Count

1508

Package Type

FC-FBGA

For Use With

544-1701 - DSP PRO KIT W/SII EP2S180N

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Lead Free Status / Rohs Status

Not Compliant

Other names

544-2164

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP2S180F1508C3

Manufacturer:

ALTERA

Quantity:

3 000

Company:

Part Number:

EP2S180F1508C3N

Manufacturer:

ALTERA

Quantity:

624

Part Number:

EP2S180F1508C3N

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

Configuration

3–8

Stratix II Device Handbook, Volume 1

Notes for

(1)

(2)

(3)

(4)

PPA

JTAG

Configuration

Table 3–5. Stratix II Configuration Features (Part 2 of 2)

Scheme

In these modes, the host system must send a DCLK that is 4× the data rate.

The enhanced configuration device decompression feature is available, while the Stratix II decompression feature

is not available.

Only remote update mode is supported when using the AS configuration scheme. Local update mode is not

supported.

The supported download cables include the Altera USB Blaster universal serial bus (USB) port download cable,

MasterBlaster serial/USB communications cable, ByteBlaster II parallel port download cable, and the

ByteBlasterMV parallel port download cable.

Table

3–5:

MAX II device or microprocessor and

flash device

Download cable

MAX II device or microprocessor and

flash device

f

Configuration Method

See the Configuring Stratix II & Stratix II GX Devices chapter in volume 2

of the Stratix II Device Handbook or the Stratix II GX Device Handbook for

more information about configuration schemes in Stratix II and

Stratix II GX devices.

Device Security Using Configuration Bitstream Encryption

Stratix II FPGAs are the industry’s first FPGAs with the ability to decrypt

a configuration bitstream using the Advanced Encryption Standard

(AES) algorithm. When using the design security feature, a 128-bit

security key is stored in the Stratix II FPGA. To successfully configure a

Stratix II FPGA that has the design security feature enabled, it must be

configured with a configuration file that was encrypted using the same

128-bit security key. The security key can be stored in non-volatile

memory inside the Stratix II device. This non-volatile memory does not

require any external devices, such as a battery back-up, for storage.

(4)

Design Security Decompression

Altera Corporation

Remote System

Upgrade

v

May 2007