ICS854104AGLF IDT, Integrated Device Technology Inc, ICS854104AGLF Datasheet

ICS854104AGLF

Specifications of ICS854104AGLF

800-1183-5

800-1183

854104AGLF

Available stocks

Related parts for ICS854104AGLF

ICS854104AGLF Summary of contents

Page 1

Low Skew, 1-to-4, Differential-to-LVDS Fanout Buffer General Description The ICS854104 is a low skew, high performance ICS 1-to-4 Differential-to-LVDS Clock Fanout Buffer and a member of the HiPerClockS™ family of High HiPerClockS™ Performance Clock Solutions from IDT. Utilizing Low Voltage ...

Page 2

ICS854104 Data Sheet Table 1. Pin Descriptions Number Name 1 OE0 Input 2 OE1 Input 3 OE2 Input 4 V Power DD 5 GND Power 6 CLK Input 7 nCLK Input 8 OE3 Input 9, 10 nQ3, Q3 Output 11, ...

Page 3

ICS854104 Data Sheet Absolute Maximum Ratings NOTE: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These ratings are stress specifications only. Functional operation of product at these conditions or any conditions beyond those ...

Page 4

ICS854104 Data Sheet Table 4D. LVDS DC Characteristics, V Symbol Parameter V Differential Output Voltage OD ∆V V Magnitude Change Offset Voltage OS ∆V V Magnitude Change OS OS Table 5. AC Characteristics Symbol Parameter ...

Page 5

ICS854104 Data Sheet Additive Phase Jitter The spectral purity in a band at a specific offset from the fundamental compared to the power of the fundamental is called the dBc Phase Noise. This value is normally expressed using a Phase ...

Page 6

ICS854104 Data Sheet Parameter Measurement Information V DD 3.3V±5% POWER SUPPLY LVDS + Float GND – 3.3V LVDS Output Load AC Test Circuit nCLK CLK nQ[0:3] Q[0: Propagation Delay nQx Qx nQy Qy tsk(o) Output Skew ICS854104AG REVISION ...

Page 7

ICS854104 Data Sheet Parameter Measurement Information, continued nQ[0:3] 80% 20% Q[0: Output Rise/Fall Time V DD LVDS DC Input Differential Output Voltage Setup ICS854104AG REVISION A AUGUST 14, 2009 80 Input 20 Offset ...

Page 8

ICS854104 Data Sheet Application Information Wiring the Differential Input to Accept Single-Ended Levels Figure 1 shows how the differential input can be wired to accept single-ended levels. The reference voltage V_REF = V generated by the bias resistors R1, R2 ...

Page 9

ICS854104 Data Sheet Differential Clock Input Interface The CLK /nCLK accepts LVDS, LVPECL, LVHSTL, SSTL, HCSL and other differential signals. Both signals must meet the V input requirements. Figures show interface examples for the HiPerClockS CLK/nCLK input ...

Page 10

ICS854104 Data Sheet 3.3V LVDS Driver Termination A general LVDS interface is shown in Figure 100Ω differential transmission line environment, LVDS drivers require a matched load termination of 100Ω across near the receiver input. 3.3V LVDS Driver ...

Page 11

ICS854104 Data Sheet Power Considerations This section provides information on power dissipation and junction temperature for the ICS854104. Equations and example calculations are also provided. 1. Power Dissipation. The total power dissipation for the ICS854104 is the sum of the ...

Page 12

ICS854104 Data Sheet Reliability Information Table 7. θ vs. Air Flow Table for a 16 Lead TSSOP JA Meters per Second Multi-Layer PCB, JEDEC Standard Test Boards Transistor Count The transistor count for ICS854104 is: 286 Pin compatible with SN65LVDS104 ...

Page 13

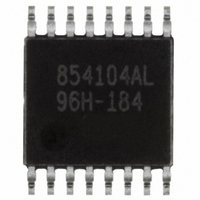

ICS854104 Data Sheet Ordering Information Table 9. Ordering Information Part/Order Number Marking 854104AG 854104AG 854104AGT 854104AG 854104AGLF 854104AL 854104AGLFT 854104AL NOTE: Parts that are ordered with an "LF" suffix to the part number are the Pb-Free configuration and are RoHS ...

Page 14

ICS854104 Data Sheet Revision History Sheet Rev Table Page Description of Change Characteristics - deleted "Bank A" test conditions from part-to-part skew row. ICS854104AG REVISION A AUGUST 14, 2009 LOW SKEW, 1-TO-4, DIFFERENTIAL-TO-LVDS FANOUT BUFFER 14 ...

Page 15

ICS854104 Datasheet 6024 Silver Creek Valley Road Sales 800-345-7015 (inside USA) San Jose, California 95138 +408-284-8200 (outside USA) Fax: 408-284-2775 www.IDT.com/go/contactIDT DISCLAIMER Integrated Device Technology, Inc. (IDT) and its subsidiaries reserve the right to modify the products and/or specifications described ...