AD678KD Analog Devices Inc, AD678KD Datasheet - Page 10

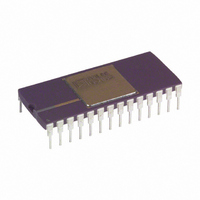

AD678KD

Manufacturer Part Number

AD678KD

Description

A/D Converter (A-D) IC

Manufacturer

Analog Devices Inc

Datasheet

1.AD678JNZ.pdf

(14 pages)

Specifications of AD678KD

No. Of Bits

12 Bit

Mounting Type

Through Hole

Features

BiMOS, High-Impedance/-Bandwidth, 10V, AC/DC

No. Of Channels

1

Interface Type

Parallel

Package / Case

28-CDIP

Rohs Status

RoHS non-compliant

Number Of Bits

12

Sampling Rate (per Second)

200k

Data Interface

Parallel

Number Of Converters

2

Power Dissipation (max)

745mw

Voltage Supply Source

Analog and Digital, Dual ±

Operating Temperature

0°C ~ 70°C

Lead Free Status / RoHS Status

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

AD678KD

Manufacturer:

ADI/亚德诺

Quantity:

20 000

AD678

OUTPUT ENABLE OPERATION

The data bits (DB11–DB0) are three-state outputs enabled by

Chip Select (CS) and Output Enable (OE). CS should be LOW

t

(HBE) are bidirectional. In 12-bit mode they are data output

bits. In 8-bit mode they are inputs which define the format of

the output register.

In unipolar mode (BIPOFF tied to AGND), the output coding

is straight binary. In bipolar mode (BIPOFF tied to REF

output coding is twos complement binary.

When EOC goes HIGH, the conversion is completed and the

output data may be read. Bringing OE LOW t

brought LOW makes the output register contents available on

the data bits. A period of time t

brought HIGH before the next SC instruction may be issued.

Figure 10 illustrates the 8-bit read mode (12/8 = LOW), where

only DB11–DB4 are used as output lines onto an 8-bit bus. The

output is read in two steps, with the high byte read first, followed

by the low byte. High Byte Enable (HBE) controls the output

sequence. The 12-bit result can be right or left justified depend-

ing on the state of R/L.

In 12-bit read mode (12/8 = HIGH), a single READ operation

accesses all 12 output bits on DB11-DB0 for interface to a

16-bit bus. Figure 11 provides the output timing relationships.

Note that t

issued at intervals closer than 5 µs. If SC is asserted sooner than

5 µs, conversion accuracy may deteriorate. For this reason, SC

should not be held LOW in an attempt to operate in a continu-

ously converting mode.

OE

before OE is brought LOW. Bits DB1 (R/L) and DB0

Figure 11. Output Timing, 12-Bit Read Mode

Figure 10. Output Timing, 8-Bit Read Mode

CR

must be observed, in that SC pulses should not be

NOTE

1

IN ASYNCHRONOUS MODE, SC IS INDEPENDENT OF CS

CD

is required after OE is

OE

after CS is

OUT

),

–10–

POWER-UP

The AD678 typically requires 10 µs after power-up to reset

internal logic.

APPLICATION INFORMATION

INPUT CONNECTIONS AND CALIBRATION

The high (10 MΩ) input impedance of the AD678 eases the

task of interfacing to high source impedances or multiplexer

channel-to-channel mismatches of up to 1000 Ω. The 10 V p-p

full-scale input range accepts the majority of signal voltages

without the need for voltage divider networks which could dete-

riorate the accuracy of the ADC.

The AD678 is factory trimmed to minimize linearity, offset and

gain errors. In unipolar mode, the only external component that

is required is a 50 Ω ± 1% resistor. Two resistors are required in

bipolar mode. If offset and gain are not critical (as in some ac

applications), even these components can be eliminated.

In some applications, offset and gain errors need to be trimmed

out completely. The following sections describe the correct pro-

cedure for these various situations.

UNIPOLAR RANGE INPUTS

Offset and gain errors can be trimmed out by using the configu-

ration shown in Figure 12. This circuit allows approximately

± 25 mV of offset trim range (± 10 LSB) and ± 0.5% of gain trim

(± 20 LSB).

The first transition (from 0000 0000 0000 to 0000 0000 0001)

should nominally occur for an input level of +1/2 LSB (1.22 mV

above ground for a 10 V range). To trim unipolar zero to this

nominal value, apply a 1.22 mV signal to AIN and adjust R1

until the first transition is located.

The gain trim is done by adjusting R2. If the nominal value is

required, apply a signal 1 1/2 LSB below full scale (9.9963 V for

a 10 V range) and adjust R2 until the last transition is located

(1111 1111 1110 to 1111 1111 1111).

If offset adjustment is not required, BIPOFF should be con-

nected directly to AGND. If gain adjustment is not required, R2

should be replaced with a fixed 50 Ω ± 1% metal film resistor. If

REF

error will be approximately 1%.

BIPOLAR RANGE INPUTS

The connections for the bipolar mode are shown in Figure 13.

In this mode, data output coding will be in twos complement

binary. This circuit will allow approximately ± 25 mV of offset

trim range (± 10 LSB) and ± 0.5% of gain trim range (20 LSB).

Either or both of the trim pots can be replaced with 50 Ω ± 1%

fixed resistors if the AD678 accuracy limits are sufficient for the

application. If the pins are shorted together, the additional offset

and gain errors will be approximately 1%.

To trim bipolar zero to its nominal value, apply a signal 1/2 LSB

below midrange (–1.22 mV for a ± 5 V range) and adjust R1

until the major carry transition is located (1111 1111 1111 to

0000 0000 0000). To trim the gain, apply a signal 1 1/2 LSB

below full scale (+4.9963 V for a ± 5 V range) and adjust R2 to

give the last positive transition (0111 1111 1110 to 0111 1111

1111). These trims are interactive so several iterations may be

necessary for convergence.

OUT

is connected directly to REF

IN

, the additional gain

REV. C