CYIS1SM1000-EVAL Cypress Semiconductor Corp, CYIS1SM1000-EVAL Datasheet - Page 13

CYIS1SM1000-EVAL

Manufacturer Part Number

CYIS1SM1000-EVAL

Description

MCU, MPU & DSP Development Tools 1M Pixel Radiation Hard CMOS Img Snsr

Manufacturer

Cypress Semiconductor Corp

Datasheet

1.CYIS1SM1000-EVAL.pdf

(24 pages)

Specifications of CYIS1SM1000-EVAL

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Figure 4 shows the timing of the pixel readout sequence.

controller presents a column address that is latched in by the rising edge of the LD_X

pulse. After decoding the X-address the column selection is clocked in the X-register

by CLK-X. The output amplifier uses the same pulse to subtract the pixel output level

from the pixel-reset level and the signal level. This causes a pipeline effect such that

the analog output of the first pixel is effectively present at the device output terminal

at the third rising edge of the X-CLK signal.

The ADC conversion starts at the falling edge of the CLK-ADC signal and produces a

valid digital output 20ns after this edge. The timing of these signals is given in

table 3.

Symbol

Cypress Semiconductor Corporation 3901 North First Street

Contact:

CLK ADC

3.2.

b

a

c

A0 … A9

D9 … D0

CLK X

Analog

LD X

output

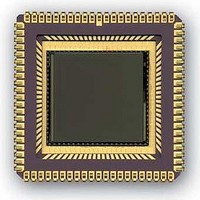

STAR-1000

Datasheet

info@Fillfactory.com

Min

40 ns

40 ns

0

Row idle time

Undefined output level

Pixel read-out timing

Typ

20 ns

Figure 4: Column selection and read-out sequence

Table 6: Timing constraints of column read out

X1

Document #:38-05714 Rev.**(Revision 6.5)

Description

Address setup time

Address valid time

ADC output valid after falling edge of CLK_ADC

X2

X3

X1

a

X4

b

X1

X2

c

X5

San Jose, CA 95134 408-943-2600

X2

X3

X6

X3

X4

The external digital

X7

X4

X5

Page 13 of 24

X8

X6