MC33696MOD434EV Freescale Semiconductor, MC33696MOD434EV Datasheet - Page 40

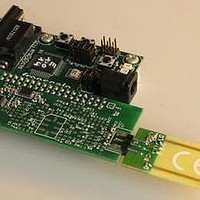

MC33696MOD434EV

Manufacturer Part Number

MC33696MOD434EV

Description

MCU, MPU & DSP Development Tools MC33696 (ECHO) RF C EVAL

Manufacturer

Freescale Semiconductor

Specifications of MC33696MOD434EV

Processor To Be Evaluated

MC9S08RG60

Interface Type

RS-232

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- Current page: 40 of 80

- Download datasheet (2Mb)

Register Description

18.2 Command Register

Figure 28

AFFC (Average Filter Frequency Control) enables direct control of the average filter cut-off frequency.

IFLA (IF Level Attenuation) controls the maximum gain of the IF amplifier in OOK modulation.

The reduction in gain can be observed if the IF amplifier AGC system is disabled (by setting RAGC = 1).

MODE selects the mode.

RSSIE (RSSI Enable) enables the RSSI function.

EDD (Envelop Detector Decay) controls the envelop detector decay.

RAGC (Reset Automatic Gain Control) resets both receiver internal AGCs.

40

Reset Value

Bit Name

Access

0 = Average filter cut-off frequency is defined by DR[1:0]

1 = Average filter cut-off frequency is defined by AFF[1:0]

0 = No effect

1 = Decreases by 20 dB (typical) the maximum gain of the IF amplifier, in OOK modulation only

0 = Receive mode

1 = Transmit mode

0 = Disabled

1 = Enabled

0 = Slow decay for minimum ripple

1 = Fast decay

0 = No action

describes the Command register, COMMAND.

AFFC

Bit 7

R/W

0

Table 14. Minimum Number of Manchester Symbols in Preamble

AFF[1:0]

IFLA

Bit 6

R/W

0

MODE

Figure 28. COMMAND Register

Bit 5

R/W

versus DR[1:0] and AFF[1:0]

0

MC33696 Data Sheet, Rev. 12

00

01

10

11

RSSIE

Bit 4

R/W

00

0

—

—

—

3

01

—

—

Bit 3

EDD

R/W

6

3

1

DR[1:0]

10

12

—

6

3

RAGC

Bit 2

R/W

0

11

24

12

6

3

FAGC

Bit 1

R/W

0

Freescale Semiconductor

BANKS

Bit 0

R

1

Addr

$03

Related parts for MC33696MOD434EV

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: