MC33696MOD434EV Freescale Semiconductor, MC33696MOD434EV Datasheet

MC33696MOD434EV

Specifications of MC33696MOD434EV

Related parts for MC33696MOD434EV

MC33696MOD434EV Summary of contents

Page 1

... OOK and FSK transmission and reception • 20 kbps maximum data rate using Manchester coding • supply voltage • Programmable via SPI • 6 kHz PLL frequency step © Freescale Semiconductor, Inc., 2006, 2007. All rights reserved. LQFP32 RSSIOUT 1 VCC2RF 2 RFIN 3 GNDLNA 4 ...

Page 2

... Transmitter: • 7.25 dBm output power • Programmable output power • FSK done by PLL programming Ordering information Temperature Range –40°C to +85°C –20°C to +85°C 2 QFN Package LQFP Package MC33696FCE/R2 MC33696FJE/R2 MC33696FCAE/R2 MC33696FJAE/R2 MC33696 Data Sheet, Rev. 9 Freescale Semiconductor ...

Page 3

... Freescale Semiconductor Figure 1. Block Diagram MC33696 Data Sheet, Rev. 9 Features 3 ...

Page 4

... Digital interface clock I/O Digital interface enable input Digital I/O ground 2 3 5.5 V input No connection Strobe oscillator capacitor or external control input Ground 2 2.7 V power supply for analog modules for decoupling capacitor RF switch control output General ground MC33696 Data Sheet, Rev. 9 Freescale Semiconductor ...

Page 5

... ESD HBM voltage capability on each pin ESD MM voltage capability on each pin Solder heat resistance test (10 s) Storage temperature Junction temperature NOTES: 1 Human body model, AEC-Q100-002 rev Machine model, AEC-Q100-003 rev. C. Freescale Semiconductor Table 2. Maximum Ratings Symbol MC33696 Data Sheet, Rev. 9 Silicon Version Value V V – ...

Page 6

... RF modules must be supplied by VCC2 by externally wiring VCC2OUT to VCC2IN, VCC2RF and VCC2VCO. 6 Symbol –40°C to +85°C V 2.7 to 3.6 CC3V V 4.5 to 5.5 CC5V V 3.0 to 3.6 CCPA MC33696 Data Sheet, Rev Temperature Range Unit –20°C to +85°C 2.1 to 3.6 V 4.5 to 5.5 V 3.0 to 3.6 V Freescale Semiconductor ...

Page 7

... LVD function is not accurate in standby mode. 8 Receiver Functional Description The receiver is based on a superheterodyne architecture with an intermediate frequency (IF) of 1.5 MHz (see Figure 1). Its input is connected to the RFIN pin. Frequency down conversion is done by a high-side Freescale Semiconductor SEB RSSIOUT 23 2 ...

Page 8

... Out-of-lock detection prevents any out-of-band emission, by stopping the transmission. The logic output SWITCH enables control of an external RF switch for isolating the two RF pins. Its output toggles when the circuit changes from receive to transmit, and vice versa. 8 MC33696 Data Sheet, Rev. 9 Freescale Semiconductor ...

Page 9

... MHz frequency band) or four times the RF frequency (for the 434 MHz and 315 MHz frequency bands). This allows the I/Q signals driving the mixer to be generated by division. 1. Refer to parameter 3.3 found in Section 19.1, “General Parameters.” Freescale Semiconductor F (Crystal F (IF REF ...

Page 10

... SCLK. This means that the clock phase and polarity control bits of the microcontroller SPI have to be CPOL = 0 and CPHA = 1 (using Freescale acronyms). Table 5 summarizes the serial digital interface feature versus the selected mode. 10 Registers”). MC33696 Data Sheet, Rev. 9 Freescale Semiconductor ...

Page 11

... N after each data byte transfer. R/W specifies the type of operation Read 1 = Write Thus, this bit is associated with the presence of information on MOSI (when writing) or MISO (when reading). Freescale Semiconductor MC33696 Digital Interface Use Figure 29), the MCU is the master node driving the SCLK Bit 5 Bit 4 ...

Page 12

... MCU. This automatic feature may be used only in receiver mode; however, if one of the register banks is related to a transmitter configuration, it may be accessed directly by programing some bits to define the active bank, thus allowing fast switching between receiver mode and transmitter mode, or between any different possible configurations. 12 NOTE MC33696 Data Sheet, Rev Freescale Semiconductor ...

Page 13

... CONFIG3 LDVS A, B CONFIG3 SOE A, B CONFIG2 RSSIx A, B RSSI Freescale Semiconductor Location Bank A Bank B Comment Bank status: indicates which register bank is active. This bit, available in Bank A and Bank B, returns the same value. Table 7. Access to Specific Bits Access R/W Available in BANKA. ...

Page 14

CONFIG1 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit Name LOF1 LOF0 CF1 CF0 RESET Reset Value R/W R/W R/W R/W R 304–434 304–315 315–434 314 No ...

Page 15

FT1-A 700701 h Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit Name FTA11 FTA10 FTA9 FTA8 FTA7 Reset Value R/W R/W R/W R/W R/W 07h FT2 Bit 7 Bit ...

Page 16

... BANKA = X, BANKB = 0 State A OFF Strobe Pin If strobe pin is 1, configuration is defined by Bank A, BANKS = 1 If strobe pin is 0, MC33696 configuration is OFF message is received during State A, current state remains State end of message. 16 State A OFF MC33696 Data Sheet, Rev. 9 Freescale Semiconductor ...

Page 17

... MCU can override strobe oscillator control by controlling strobe pin level. If MCU I/O port is in high impedance, strobe oscillator will control the OFF/ON state of the MC33696. The various available sequences are described in the following subsections. Freescale Semiconductor State B OFF MC33696 Data Sheet, Rev. 9 ...

Page 18

... If a message is being received during State current state remains State end of message. 18 State A OFF State B OFF OFF StateA StateB B OFF A B MC33696 Data Sheet, Rev. 9 State A State B OFF OFF A B Freescale Semiconductor ...

Page 19

... DSREF = 1 — In the case of FSK modulation, the data slicer reference voltage to settle — Clock recovery The preamble content must be defined carefully, to ensure that it will not be decoded as the ID or the header. Figure 8 defines the preamble in OOK and FSK modulation. Freescale Semiconductor Figure 7 ...

Page 20

... Data Slicer Reference Settling Time At Least 3 Manchester 0 Symbols at Data Rate (2 and 3) Clock Recovery ID 1 Manchester 0 Symbol at Data Rate (3) Figure 8. Preamble Definition Preamble Figure 9. Complete Message Example MC33696 Data Sheet, Rev. 9 Clock Recovery ID 1 Manchester 0 Symbol at Data Rate ( Header Data EOM Freescale Semiconductor ...

Page 21

... Figure 10. Complete Telegram with ID Detection RF Signal Receiver On Status On Time SPI Output Figure 11. Complete Telegram with Tone Detection 12.4 Receiver Startup Delay As shown in Figure 12, a settling time is required when entering the on state. Freescale Semiconductor NOTE ID P+Header P+ID P+ID P+ID P+ID Off Off Time ID Detected Tone Off ...

Page 22

... MC33696 Features versus DME Digital Interface Use Data Format SPI deselected Bit stream No clock SPI master Data bytes when CONFB = 1 Recovered clock MC33696 Data Sheet, Rev Settling Time Detected Section 15.2, “Receive Mode.” Output MOSI — MOSI SCLK Freescale Semiconductor ID ...

Page 23

... Cycling Period 15 Communication in Transmit and Receive Mode 15.1 Transmit Mode The SPI is deselected. The MC33696 receives the telegram to transmit on the MOSI line (see SEB MOSI (Input) Freescale Semiconductor (see Table 20; begins after the crystal oscillator has started), digclk + MIN (T Strobe Strobe 21) ...

Page 24

... At the IF filter output, a progressive compression logarithmic amplifier measures the input signal, ranging from the sensitivity level up to –50 dBm. 24 20) and Section 17.3, “Frequency Figure 15 shows a typical transfer MC33696 Data Sheet, Rev. 9 Registers,” for more details about Freescale Semiconductor ...

Page 25

... As a single convertor is used for the two analog signals, the RSSI register content is updated diglck timebase. digclk If RSSIE is reset, the whole RSSI module is switched off, reducing the current consumption. The output buffer connected to RSSIOUT is set to high impedance. Freescale Semiconductor Register”). LNA AGC Out D1 R1 Σ C1 Figure 16 ...

Page 26

... MOSI MISO 26 digclk . Therefore, the minimum duration of the high pulse on digclk Open Closed Updated Sampled and Hold RSSI Voltage Sampling CMD Figure 17. RSSI Operation in Sample Mode MC33696 Data Sheet, Rev released closed when RSSIC Closed Open Frozen RSSI Value Freescale Semiconductor ...

Page 27

... At power-on, the POR resets all registers to a known value (in the shaded rows in the following tables). This defines the MC33696’s default configuration. After POR, CONFB forces a low level. Therefore, an external pullup resistor is required to avoid entering configuration mode. Freescale Semiconductor Configuration, Command, and Status Registers , S1 is opened closed when RSSIC digclk ...

Page 28

... DATACLK outputs F 28 Bit 5 Bit 4 Bit 3 CF1 CF0 RESET Figure 19. CONFIG1 Register LOF1 LOF0 Transceiver Function Level on SWITCH Receiving Transmitting Transmitting Receiving NOTE dataclk MC33696 Data Sheet, Rev. 9 Bit 2 Bit 1 Bit 0 SL LVDE CLKE CF1 CF0 Low High Low High Freescale Semiconductor Addr $00 ...

Page 29

... If the data manager is disabled, the incoming signal data rate must be lower than or equal to the data manager maximum data rate. TRXE (Transceiver Enable) enables the whole transceiver standby mode 1 = other modes can be activated DME (Data Manager Enable) enables the data manager disabled 1 = enabled Freescale Semiconductor Configuration, Command, and Status Registers Bit 5 Bit 4 Bit 3 MODU DR1 DR0 ...

Page 30

... Table 12. RF Input Level Attenuation RF Input Level ILA0 Attenuation Table 13. RF Output Level Attenuation RF Output Level OLA0 Attenuation MC33696 Data Sheet, Rev. 9 Bit 2 Bit 1 Bit 0 Addr ILA0 OLA1 OLA0 $ See Parameter Number 2.5 2.6 2.7 2.8 See Parameter Number 4.20 4.3 4.4 4.5 Freescale Semiconductor ...

Page 31

... IFLA (IF Level Attenuation) controls the maximum gain of the IF amplifier in OOK modulation effect 1 = Decreases (typical) the maximum gain of the IF amplifier, in OOK modulation only The reduction in gain can be observed if the IF amplifier AGC system is disabled (by setting RAGC = 1). MODE selects the mode. Freescale Semiconductor Table 14. Average Filter Cut-off Frequency Average Filter Cut-off AFF0 Frequency ...

Page 32

... Bit Name FSK3 FSK2 Reset Value 0 1 Bit 7 Bit 6 Bit Name F7 F6 Reset Value Bit 13 Bit 12 Bit 11 FSK1 FSK0 F11 Bit 5 Bit 4 Bit Figure 23. F Register MC33696 Data Sheet, Rev. 9 Bit 10 Bit 9 Bit 8 Addr F10 Bit 2 Bit 1 Bit Freescale Semiconductor $04 $05 ...

Page 33

... Table 17. Frequency Numerical Example (434 MHz Band) FSK[3:0] Then, two frequencies are calculated internally, as follows. = F[11:0] - Δf to transmit a logical 0 — F carrier0 = F[11:0] + Δf to transmit a logical 1 — F carrier1 FTA[11:0] and FTB[11:0] are not used Freescale Semiconductor Bit 21 Bit 20 Bit 19 FTA9 FTA8 FTA7 ...

Page 34

... Bit 3 RON2 RON1 RON0 Figure 25. RXONOFF Register Table 20. Receiver On Time Definition Receiver On Time 512 x T 0000 Forbidden value 0001 1 0010 2 ... ... MC33696 Data Sheet, Rev. 9 Frequency Resolution (Hz) F /4096 ref F /2048 ref Bit 2 Bit 1 Bit 0 ROFF2 ROFF1 ROFF0 digclk Freescale Semiconductor Addr $09 ...

Page 35

... IDL[1:0] (Identifier Length) sets the length of the identifier, as shown on ID[5:0] (Identifier) sets the identifier. The ID is Manchester coded. Its LSB corresponds to the register’s LSB, whatever the specified length. Figure 27 defines the Header register, HEADER. Freescale Semiconductor Table 20. Receiver On Time Definition Receiver On Time 512 x T 1111 15 Table 21 ...

Page 36

... HDL1 HDL0 HD Length Bit 5 Bit 4 Bit 3 RSSI5 RSSI4 RSSI3 Figure 28. RSSI Register MC33696 Data Sheet, Rev. 9 Bit 2 Bit 1 Bit 0 HD2 HD1 HD0 Table 23. 1 bits 2 bits 4 bits 6 bits Bit 2 Bit 1 Bit 0 RSSI2 RSSI1 RSSI0 overview is presented in digclk Freescale Semiconductor Addr $0B Addr $0C ...

Page 37

... Standby/LVD mode to configuration mode. STROBE CONFB SPI Startup Time SEB Figure 30. First Valid Sequence from Standby/LVD Mode to Configuration Mode Freescale Semiconductor Figure 33 and Figure 29) and configuration registers’ content is set to the reset State 30 Active Bank Change ...

Page 38

... STROBE = 1 Figure 32. Receive Mode, DME = 0, SOIE = μs (Maximum) NOTE Figure 32 shows the state diagram. STROBE = 0 STROBE = 0 State 0 Off Off Counter = ROFF[2:0] or STROBE = 1 On Counter = RON[3:0] and STROBE ≠ 1 State 0b On Raw Data on MOSI MC33696 Data Sheet, Rev. 9 SPI Deselected Freescale Semiconductor ...

Page 39

... RON time, if STROBE≠1. State 12 its complement has been detected. The data manager is now waiting for a header or its complement. If neither a header, nor its complement, has been received before a time-out of 256 bits at data rate, the system returns to state 10. Freescale Semiconductor Figure 33 STROBE = 0 State 5 ...

Page 40

... ID Detected State 12 On Waiting for a Valid Header Header Received State 13 On Output Data and Clock Waiting for End of Message EOM Received and STROBE ≠ 1 Figure 34. Receive Mode, DME = 1, SOE = 1 MC33696 Data Sheet, Rev. 9 STROBE = 0 STROBE = 1 EOM Received and STROBE = 1 Freescale Semiconductor ...

Page 41

... STROBE is high. State 23: A header or its complement has been received; data and clock signals are output on the SPI port until an EOM indicates the end of the data sequence. If the complement of the header has been received, Freescale Semiconductor STROBE = 0 State 20 ...

Page 42

... Lock time parameter 0 or lock time parameter 5.1 or lock time parameter 5 lock time parameter 5.1 or lock time parameter 5.9 Message.” MC33696 Data Sheet, Rev. 9 Receiver Receiver Preamble On-to-Off Time, 1 Time Parameter 1.12 √ 5.9 √ 5.9 √ √ √ Freescale Semiconductor ...

Page 43

... Typical values reflect average measurement at V Parameter 2.2 OOK sensitivity at 315 MHz DME = 1, DSREF = 4.8 kbps, PER = 0.1 2.40 OOK sensitivity at 434 MHz DME = 1, DSREF = 4.8 kbps, PER = 0.1 Freescale Semiconductor Table 3. Values refer to the circuit recommended in the application Test Conditions Comments Receiver on ...

Page 44

... Freescale Semiconductor ...

Page 45

... Figure 36. OOK Sensitivity Variation Versus Temperature Freescale Semiconductor Table 3. Values refer to the circuit recommended in the application Test Conditions, Comments Min 20 15 OOK Sensitivity Variation vs Temperature (Ref : 3V, 25°C, 4800bps) 315 MHz 434 MHz ...

Page 46

... Voltage (V) FSK Sensitivity Variation vs Temperature (Ref : 3V, 25°C, +/-64kHz, 4800 bps ) 315 MHz 434 MHz 868 MHz 916 MHz 25°C Temperature (°C) MC33696 Data Sheet, Rev. 9 315 MHz 434 MHz 868 MHz 916 MHz 3.6 V 85°C Freescale Semiconductor ...

Page 47

... Figure 39. FSK Sensitivity Variation Versus Voltage 2400 Figure 40. OOK Sensitivity Variation Versus Data Rate Freescale Semiconductor FSK Sensitivity Variation vs Voltage (Ref : 3V, 25°C, +/-64kHz, 4800bps ) 315 MHz 434 MHz 868 MHz 916 MHz 2 Voltage (V) Sensitivity Variation Versus Data Rate (Ref : 25°C, 3V, 434MHz , OOK, 4800bps) ...

Page 48

... Figure 42. FSK Sensitivity Variation Versus Frequency Deviation 48 Sensitivity Variation vs Data Rate (Ref : 25°C, 3V, 434MHz , FSK +/-64kHz, 4800bps) 4800 Data Rate (bps) Sensitivity Variation vs Frequency Deviation 100 110 Frequency Deviation (kHz) MC33696 Data Sheet, Rev. 9 9600 19200 120 130 140 150 160 170 Freescale Semiconductor ...

Page 49

... Digital RSSI Registers for Input signal @–24 dBm 19.4 Transmitter: RF Parameters RF parameters assume a matching network between test equipment and the D.U.T, and apply to all bands unless otherwise specified. Freescale Semiconductor Table 3. Values refer to the circuit recommended in the application Test Conditions Comments Refer to Section 10, “ ...

Page 50

... Freescale Semiconductor ...

Page 51

... Figure 43. Output Power Versus Temperature Freescale Semiconductor Table 3. Values refer to the circuit recommended in the application Test Conditions Min Comments (FCE, FJE) OLA[1:0] = 00, TX mode — OLA[1:0] = 00, TX mode — OLA[1:0] = 00, TX mode — ...

Page 52

... MHz 916 MHz Limits Min Typ Max — 50 100 — 30 — — 58 — — 248 — — 160 — — 278 — — 0.6 1.2 — — 120 Freescale Semiconductor = 25°C. A Unit μs μs kHz kHz kHz kHz ms Ω ...

Page 53

... Input low voltage 7.11 Input high voltage 7.12 Input hysteresis 7.5 Sink current 7.6 NOTES: 1 Input levels of those pins are referenced Input levels of those pins are referenced to V Freescale Semiconductor Table 3. Values refer to the circuit recommended in the application Test Conditions Comments .C3 Strobe With 1% resistor R13 With 1% resistor R13 & ...

Page 54

... V CC — — 3 Limits Min Typ Max 1 — — 20 — — — — digclk 100 — — 1 100 — — — — digclk — — 100 120 — — 100 — — . Freescale Semiconductor = 25°C. A Unit 25°C. A Unit μ ...

Page 55

... Figure 46. Digital Interface Timing Diagram in Receive Mode (DME = 1) Examples of crystal characteristics are given in Table 25. Typical Crystal Reference and Characteristics LN-G102-1183 Parameter NX5032GA Frequency Load capacitance ESR Freescale Semiconductor 9.9 Table 25. Reference & Type 315 MHz 434 MHz LN-G102-1182 NX5032GA 17.5814 24 ...

Page 56

... VCC2 4 C6 GNDLNA 5 MC33696 VCC2VCO 6 C22 GNDPA1 7 RFOUT 8 GNDPA2 C24 X1 C29 C35 MC33696 Data Sheet, Rev. 9 RSSIOUT STROBE GND 24 SEB SEB 23 SCLK SCLK 22 MOSI MOSI 21 MISO MISO U4 20 CONFB CONFB 19 DATACLK DATACLK 18 RSSIC RSSIC 17 GNDDIG VCC2 C30 R13 C31 Freescale Semiconductor ...

Page 57

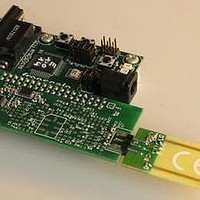

... MC33696 RF Modules available for MC33696 evaluation. Matching networks should be retuned if any change is made to the PCB (track width, length or place, or PCB thickness, or component value). Never use, as is, a matching network designed for another PCB. Freescale Semiconductor NOTE MC33696 Data Sheet, Rev. 9 Application Schematics ...

Page 58

... Case Outline Dimensions 21 Case Outline Dimensions 21.1 LQFP32 Case 58 MC33696 Data Sheet, Rev. 9 Freescale Semiconductor ...

Page 59

... Freescale Semiconductor MC33696 Data Sheet, Rev. 9 Case Outline Dimensions 59 ...

Page 60

... Case Outline Dimensions 60 MC33696 Data Sheet, Rev. 9 Freescale Semiconductor ...

Page 61

... QFN32 Case Freescale Semiconductor MC33696 Data Sheet, Rev. 9 Case Outline Dimensions 61 ...

Page 62

... Case Outline Dimensions 62 MC33696 Data Sheet, Rev. 9 Freescale Semiconductor ...

Page 63

... Freescale Semiconductor MC33696 Data Sheet, Rev. 9 Case Outline Dimensions 63 ...

Page 64

... Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer ...