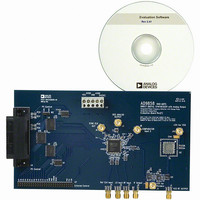

AD9858/PCBZ Analog Devices Inc, AD9858/PCBZ Datasheet

AD9858/PCBZ

Specifications of AD9858/PCBZ

AD9858/PCB

Related parts for AD9858/PCBZ

AD9858/PCBZ Summary of contents

Page 1

... Included within is information on system requirements, installing the evaluation software, menus and buttons, and window environments. Documentation for the other boards (fractional-divide loop and translation loop) is also accessible from the Design Tools section of the Analog Devices DDS homepage: www.analog.com/dds. AD9858 DDS ...

Page 2

AD9858PCB TABLE OF CONTENTS Equipment ..................................................................................... 3 Installing from the CD................................................................. 3 Installing from the Web ............................................................... 3 Main Program Window............................................................... 3 Buttons ........................................................................................... 4 Menus............................................................................................. 4 Control Window........................................................................... 5 I/O Interface.................................................................................. 6 REVISION HISTORY Revision 0: Initial Version PLL ...

Page 3

... From your browser www.analog.com/dds. 2. Click the product selection guide link. 3. Click the AD9858 link, then click the design tools link. 4. Click the install evaluation software link and follow the instructions that appear. After starting the AD9858 evaluation software, the main program window appears. At the top of the screen are the File, PC I/O, View, and Help menus and the Load Setup, Save Setup, Reset, I/O Config, and FUD buttons ...

Page 4

AD9858PCB BUTTONS The main program window has these buttons: • The Load Setup and Save Setup buttons load a setup file and save the current setup to a setup file. • The Reset button issues a master reset to the ...

Page 5

CONTROL WINDOW The control window allows the user to set many of the operating parameters of the device. In the Clock pane, the user can specify the current clock frequency supplied to the device. If the user desires, the clock ...

Page 6

AD9858PCB I/O INTERFACE This window is where the user specifies whether the evaluation board is to communicate with the AD9858 device in parallel or serial mode. In serial mode, the user can also specify LSB first or last as well ...

Page 7

PLL FAST LOCK This window is accessible from the Control window or from the View menu. The PLL Fast Lock window allows the user to enable and disable the PLL Fast Lock algorithm. When engaged, the charge pump operates in ...

Page 8

AD9858PCB PROFILES WINDOW The AD9858 has four user-defined profiles (segments of memory). Each profile can be programmed with a different frequency tuning word and phase adjustment word. As shown in Figure 12, users can click the Edit button next to ...

Page 9

FREQUENCY SWEEP SETUP DIALOG BOXES At the bottom of the Profiles window is the display for the frequency sweeping mode variables—Delta Frequency Tuning Word and Ramp Rate. Clicking the Edit button opens a dialog window that assists the user in ...

Page 10

AD9858PCB READBACK WINDOW When the READBACK button is clicked, the evaluation software polls and displays the current contents of all internal memory registers. When the CLEAR button is clicked, a master reset is issued and all internal memory registers are ...

Page 11

USING EVALUATION SOFTWARE WITH THE DAC OUTPUT BOARD As mentioned in the Circuit Overview section, the AD9858 cannot operate at speeds greater than 1 GHz. It can accept clocks from 1 GHz to 2 GHz, but the ...

Page 12

AD9858PCB ORDERING GUIDE Model Package Description AD9858/PCB Frequency Synthesizer Board © 2004 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D04430-0-1/04(0) Rev Page ...