M24LR64-RMB6T/2 STMicroelectronics, M24LR64-RMB6T/2 Datasheet - Page 34

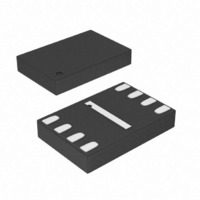

M24LR64-RMB6T/2

Manufacturer Part Number

M24LR64-RMB6T/2

Description

13.56MHZ 64KBIT EEPROM UFDFPN8

Manufacturer

STMicroelectronics

Datasheet

1.M24LR64-RMB6T2.pdf

(128 pages)

Specifications of M24LR64-RMB6T/2

Featured Product

STM32 Cortex-M3 Companion Products

Rf Type

Read / Write

Frequency

13.56MHz

Features

64 Kbit EEPROM

Package / Case

8-MLP, 8-UFDFPN

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

497-10485-2

M24LR64-RMR6T/2

M24LW64-RMB6T/2

M24LR64-RMR6T/2

M24LW64-RMB6T/2

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 34 of 128

- Download datasheet (2Mb)

I

5.9

34/128

2

C device operation

Minimizing system delays by polling on ACK

During the internal write cycle, the device disconnects itself from the bus, and writes a copy

of the data from its internal latches to the memory cells. The maximum I²C write time (t

shown in

can be used by the bus master.

The sequence, as shown in

1.

2.

3.

Initial condition: a write cycle is in progress.

Step 1: the bus master issues a Start condition followed by a device select code (the

first byte of the new instruction).

Step 2: if the device is busy with the internal Write cycle, no Ack will be returned and

the bus master goes back to Step 1. If the device has terminated the internal write

cycle, it responds with an Ack, indicating that the device is ready to receive the second

part of the instruction (the first byte of this instruction having been sent during Step 1).

Table 104

, but the typical time is shorter. To make use of this, a polling sequence

Figure

Doc ID 15170 Rev 12

12, is:

M24LR64-R

w

) is

Related parts for M24LR64-RMB6T/2

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

64 Kbit EEPROM with password protection & dual interface: 400kHz I�C serial bus & ISO 18000-3 mode 1 RF protocol at 13.56MHz

Manufacturer:

STMICROELECTRONICS [STMicroelectronics]

Datasheet:

Part Number:

Description:

64 Kbit Eeprom With Password Protection & Dual Interface 400 Khz I?c Serial Bus & Iso 15693 Rf Protocol At 13.56 Mhz

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

13.56MHZ 64KBIT EEPROM SO8N

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

64 Kbit EEPROM with password protection & dual interface

Manufacturer:

STMICROELECTRONICS [STMicroelectronics]

Datasheet:

Part Number:

Description:

13.56MHZ 64KBIT EEPROM 8 TSSOP

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

EEPROM Dual Interface 64k EEPROM ISO15693-I2C

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

EEPROM, 64K, DUAL INTERFACE, 8TSSOP

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

EEPROM, 64K, DUAL INTERFACE, 8SOIC

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

STMicroelectronics [RIPPLE-CARRY BINARY COUNTER/DIVIDERS]

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

STMicroelectronics [LIQUID-CRYSTAL DISPLAY DRIVERS]

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

BOARD EVAL FOR MEMS SENSORS

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

NPN TRANSISTOR POWER MODULE

Manufacturer:

STMicroelectronics

Datasheet: