AT90PWM81-16SF Atmel, AT90PWM81-16SF Datasheet - Page 238

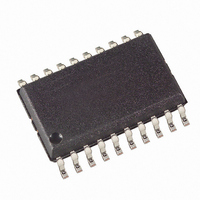

AT90PWM81-16SF

Manufacturer Part Number

AT90PWM81-16SF

Description

IC MCU AVR 8K FLASH ISP 20SOIC

Manufacturer

Atmel

Series

AVR® 90PWM Lightingr

Datasheet

1.AT90PWM81-16MN.pdf

(325 pages)

Specifications of AT90PWM81-16SF

Core Processor

AVR

Core Size

8-Bit

Speed

16MHz

Connectivity

SPI

Peripherals

Brown-out Detect/Reset, PWM, WDT

Number Of I /o

16

Program Memory Size

8KB (8K x 8)

Program Memory Type

FLASH

Eeprom Size

512 x 8

Ram Size

256 x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 8x10b; D/A 1x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 105°C

Package / Case

20-SOIC (7.5mm Width)

For Use With

ATSTK600-SOIC - STK600 SOCKET/ADAPTER FOR SOIC

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

AT90PWM81-16SF

Manufacturer:

Atmel

Quantity:

2 428

- Current page: 238 of 325

- Download datasheet (6Mb)

20.5.1

238

AT90PWM81

Store Program Memory Control and Status Register – SPMCSR

The Store Program Memory Control and Status Register contains the control bits needed to control the

Boot Loader operations.

• Bit 7 – SPMIE: SPM Interrupt Enable

When the SPMIE bit is written to one, and the I-bit in the Status Register is set (one), the SPM ready inter-

rupt will be enabled. The SPM ready Interrupt will be executed as long as the SPMEN bit in the SPMCSR

Register is cleared.

• Bit 6 – RWWSB: Read-While-Write Section Busy

When a Self-Programming (Page Erase or Page Write) operation to the RWW section is initiated, the

RWWSB will be set (one) by hardware. When the RWWSB bit is set, the RWW section cannot be

accessed. The RWWSB bit will be cleared if the RWWSRE bit is written to one after a Self-Programming

operation is completed. Alternatively the RWWSB bit will automatically be cleared if a page load opera-

tion is initiated.

• Bit 5 – SIGRD: Signature Row Read

If this bit is written to one at the same time as SPMEN, the next LPM instruction within three clock cycles

will read a byte from the signature row into the destination register. see

Software243“ for details.

An SPM instruction within four cycles after SIGRD and SPMEN are set will have no effect. This opera-

tion is reserved for future use and should not be used.

• Bit 4 – RWWSRE: Read-While-Write Section Read Enable

When programming (Page Erase or Page Write) to the RWW section, the RWW section is blocked for

reading (the RWWSB will be set by hardware). To re-enable the RWW section, the user software must

wait until the programming is completed (SPMEN will be cleared). Then, if the RWWSRE bit is written

to one at the same time as SPMEN, the next SPM instruction within four clock cycles re-enables the

RWW section. The RWW section cannot be re-enabled while the Flash is busy with a Page Erase or a

Page Write (SPMEN is set). If the RWWSRE bit is written while the Flash is being loaded, the Flash load

operation will abort and the data loaded will be lost.

• Bit 3 – BLBSET: Boot Lock Bit Set

If this bit is written to one at the same time as SPMEN, the next SPM instruction within four clock cycles

sets Boot Lock bits and Memory Lock bits, according to the data in R0. The data in R1 and the address in

the Z-pointer are ignored. The BLBSET bit will automatically be cleared upon completion of the Lock bit

set, or if no SPM instruction is executed within four clock cycles.

An LPM instruction within three cycles after BLBSET and SPMEN are set in the SPMCSR Register, will

read either the Lock bits or the Fuse bits (depending on Z0 in the Z-pointer) into the destination register.

See

• Bit 2 – PGWRT: Page Write

Bit

Read/Write

Initial Value

“Reading the Fuse and Lock Bits from Software” on page 242

7

SPMIE

R/W

0

6

RWWSB

R

0

5

SIGRD

R/W

0

4

RWWSRE

R/W

0

3

BLBSET

R/W

0

2

PGWRT

R/W

0

for details.

Reading the Signature Row from

1

PGERS

R/W

0

0

SPMEN

R/W

0

7734P–AVR–08/10

SPMCSR

Related parts for AT90PWM81-16SF

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Atmel Corporation

Datasheet:

Part Number:

Description:

IC MCU AVR 8K FLASH ISP 20SOIC

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC MCU AVR 8K FLASH ISP 32QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC MCU AVR 8K FLASH ISP 32QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

8-bit Avr Microcontroller With 8k Bytes In- System Programmable Flash

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Monolithic Integrated Feature Phone Circuit

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Multistandard Video-IF and Quasi Parallel Sound Processing

Manufacturer:

ATMEL Corporation

Datasheet: