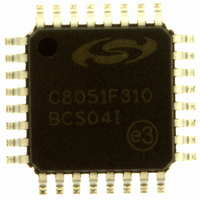

C8051F310-GQ Silicon Laboratories Inc, C8051F310-GQ Datasheet - Page 149

C8051F310-GQ

Manufacturer Part Number

C8051F310-GQ

Description

IC 8051 MCU 16K FLASH 32LQFP

Manufacturer

Silicon Laboratories Inc

Series

C8051F31xr

Datasheets

1.C8051F310-TB.pdf

(228 pages)

2.C8051F310-TB.pdf

(2 pages)

3.C8051F310-GQ.pdf

(218 pages)

Specifications of C8051F310-GQ

Core Size

8-Bit

Program Memory Size

16KB (16K x 8)

Oscillator Type

Internal

Core Processor

8051

Speed

25MHz

Connectivity

SMBus (2-Wire/I²C), SPI, UART/USART

Peripherals

POR, PWM, Temp Sensor, WDT

Number Of I /o

29

Program Memory Type

FLASH

Ram Size

1.25K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.6 V

Data Converters

A/D 21x10b

Operating Temperature

-40°C ~ 85°C

Package / Case

32-LQFP

No. Of I/o's

29

Ram Memory Size

1280Byte

Cpu Speed

25MHz

No. Of Timers

4

No. Of Pwm Channels

5

Digital Ic Case

RoHS Compliant

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

770-1006 - ISP 4PORT FOR SILABS C8051F MCU336-1445 - ADAPTER PROGRAM TOOLSTICK F310336-1329 - KIT REF DESIGN SENSORLESS BLDC336-1253 - DEV KIT FOR C8051F310/F311

Eeprom Size

-

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

336-1252

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

C8051F310-GQ

Manufacturer:

SiliconL

Quantity:

4 998

Company:

Part Number:

C8051F310-GQ

Manufacturer:

SILICON

Quantity:

411

Company:

Part Number:

C8051F310-GQ

Manufacturer:

Silicon Laboratories Inc

Quantity:

10 000

Part Number:

C8051F310-GQ

Manufacturer:

SILICONLABS原装

Quantity:

20 000

Company:

Part Number:

C8051F310-GQR

Manufacturer:

SILICON

Quantity:

3 300

Company:

Part Number:

C8051F310-GQR

Manufacturer:

SILICON41

Quantity:

120

Company:

Part Number:

C8051F310-GQR

Manufacturer:

Silicon Laboratories Inc

Quantity:

10 000

Part Number:

C8051F310-GQR

Manufacturer:

SILICON LABS/芯科

Quantity:

20 000

14.4. Using the SMBus

The SMBus can operate in both Master and Slave modes. The interface provides timing and shifting con-

trol for serial transfers; higher level protocol is determined by user software. The SMBus interface provides

the following application-independent features:

•

•

•

•

•

•

•

SMBus interrupts are generated for each data byte or slave address that is transferred. When transmitting,

this interrupt is generated after the ACK cycle so that software may read the received ACK value; when

receiving data, this interrupt is generated before the ACK cycle so that software may define the outgoing

ACK value. See

sequences.

Interrupts are also generated to indicate the beginning of a transfer when a master (START generated), or

the end of a transfer when a slave (STOP detected). Software should read the SMB0CN (SMBus Control

register) to find the cause of the SMBus interrupt. The SMB0CN register is described in

“14.4.2. SMB0CN Control Register” on page

ence.

SMBus configuration options include:

•

•

•

•

These options are selected in the SMB0CF register, as described in

tion Register” on page

Byte-wise serial data transfers

Clock signal generation on SCL (Master Mode only) and SDA data synchronization

Timeout/bus error recognition, as defined by the SMB0CF configuration register

START/STOP timing, detection, and generation

Bus arbitration

Interrupt generation

Status information

Timeout detection (SCL Low Timeout and/or Bus Free Timeout)

SDA setup and hold time extensions

Slave event enable/disable

Clock source selection

Section “14.5. SMBus Transfer Modes” on page 157

150.

153; Table 14.4 provides a quick SMB0CN decoding refer-

Rev. 1.7

C8051F310/1/2/3/4/5/6/7

Section “14.4.1. SMBus Configura-

for more details on transmission

Section

149