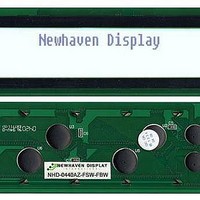

NHD-0440AZ-FSW-FBW Newhaven Display, NHD-0440AZ-FSW-FBW Datasheet - Page 8

NHD-0440AZ-FSW-FBW

Manufacturer Part Number

NHD-0440AZ-FSW-FBW

Description

LCD MOD CHAR 4X40 WH TRANSFL

Manufacturer

Newhaven Display

Series

NHD-0440AZ-Fr

Datasheet

1.NHD-0440AZ-FSW-FBW.pdf

(11 pages)

Specifications of NHD-0440AZ-FSW-FBW

Display Type

FSTN - Film Super-Twisted Nematic

Display Mode

Transflective

Number Of Digits/alpha

160

Outline L X W X H

190.00mm x 54.00mm x 9.50mm

Viewing Area

147.00mm L x 29.50mm W

Backlight

LED - White

Display Format

40 x 4

Character Size

4.89mm H x 2.78mm W

Character Format

5 x 8 Dots

Voltage - Supply

5.0V

Dot Size

0.50mm W x 0.55mm H

Operating Temperature

-20°C ~ 70°C

Character Count X Line

40 x 4

Module Size (w X H X T)

190 mm x 54 mm x 13 mm

Fluid Type

FSTN Negative

Voltage Rating

5 V

Operating Temperature Range

- 20 C to + 70 C

Backlight Type

LED Yellow / Green

Interface

Parallel

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

NHD-0440AZ

F: Display line number control bit

When F=“Low”, 5x8 dots format display mode is set.

When F=“High”, 5x11 dots format display mode.

Set CGRAM address to AC.

The instruction makes CGRAM data available from MPU.

Set DDRAM address to AC.

This instruction makes DDRAM data available form MPU.

When 1-line display mode (N=LOW), DDRAM address is form “00H” to “4FH”.

In 2-line display mode (N=High), DDRAM address in the 1

In the 2

This instruction shows whether KS0066U is in internal operation or not.

If the resultant BF is “High”, internal operation is in progress and should wait BF is to be LOW, which by then if the nest

instruction can be performed. In this instruction you can also read the value of the address counter.

Write binary 8-bit data to DDRAM/CGRAM.

The selection of RAM from DDRAM, and CGRAM, is set by the previous address set instruction (DDRAM address set,

CGRAM address set).

RAM set instruction can also determine the AC direction to RAM.

After write operation. The address is automatically increased/decreased by 1, according to the entry mode.

Read binary 8-bit data from DDRAM/CGRAM.

The selection of RAM is set by the previous address set instruction. If the address set instruction of RAM is not

performed before this instruction, the data that has been read first is invalid, as the direction of AC is not yet determined.

If RAM data is read several times without RAM address instructions set before, read operation, the correct RAM data

can be obtained from the second. But the first data would be incorrect, as there is no time margin to transfer RAM data.

In case of DDRAM read operation, cursor shift instruction plays the same role as DDRAM address set instruction,

It also transfers RAM data to output data register.

After read operation, address counter is automatically increased/decreased by 1 according to the entry mode.

V: A

7)

8)

9)

10) Write data to RAM

11) Read data from RAM

RS

RS

RS

RS

RS

nd

0

0

0

1

1

Set CGRAM address

Set DDRAM address

Read busy flag & address

line is from “40H” to “67H”.

R/W

R/W

R/W

R/W

R/W

0

0

1

0

1

DB7

DB7

DB7

DB7

DB7

BF

D7

D7

0

1

DB6

DB6

DB6

DB6

DB6

AC6

AC6

D6

D6

1

DB5

AC5

DB5

AC5

DB5

AC5

DB5

DB5

D5

D5

7/9

st

line form “00H” to “27H”, and DDRAM address

DB4

AC4

DB4

AC4

DB4

AC4

DB4

DB4

D4

D4

DB3

AC3

DB3

AC3

DB3

AC3

DB3

DB3

D3

D3

DB2

AC2

DB2

AC2

DB2

AC2

DB2

DB2

D2

D2

DB1

DB1

DB1

DB1

DB1

AC1

AC1

AC1

D1

D1

01/31/2007

DB0

AC0

DB0

AC0

DB0

AC0

DB0

DB0

D0

D0