AT25DF021-MH-T Atmel, AT25DF021-MH-T Datasheet - Page 20

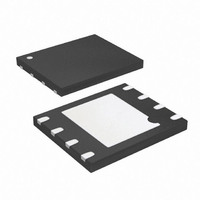

AT25DF021-MH-T

Manufacturer Part Number

AT25DF021-MH-T

Description

IC FLASH 2MBIT 70MHZ 8UDFN

Manufacturer

Atmel

Datasheet

1.AT25DF021-SSH-B.pdf

(41 pages)

Specifications of AT25DF021-MH-T

Format - Memory

FLASH

Memory Type

DataFLASH

Memory Size

2M (256K x 8)

Speed

70MHz

Interface

SPI, 3-Wire Serial

Voltage - Supply

2.7 V ~ 3.6 V

Operating Temperature

-40°C ~ 85°C

Package / Case

8-UDFN

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

location of the OTP Security Register to begin programming at. Since the size of the user-pro-

grammable portion of the OTP Security Register is 64 bytes, the upper order address bits do not

need to be decoded by the device. Therefore, address bits A23-A6 will be ignored by the device

and their values can be either a logical “1” or “0”. After the address bytes have been clocked in,

data can then be clocked into the device and will be stored in the internal buffer.

If the starting memory address denoted by A23-A0 does not start at the beginning of the OTP

Security Register memory space (A5-A0 are not all 0), then special circumstances regarding

which OTP Security Register locations to be programmed will apply. In this situation, any data

that is sent to the device that goes beyond the end of the 64-byte user-programmable space will

wrap around back to the beginning of the OTP Security Register. For example, if the starting

address denoted by A23-A0 is 00003Eh, and three bytes of data are sent to the device, then the

first two bytes of data will be programmed at OTP Security Register addresses 00003Eh and

00003Fh while the last byte of data will be programmed at address 000000h. The remaining

bytes in the OTP Security Register (addresses 000001h through 00003Dh) will not be pro-

grammed and will remain in the erased state (FFh). In addition, if more than 64 bytes of data are

sent to the device, then only the last 64 bytes sent will be latched into the internal buffer.

When the CS pin is deasserted, the device will take the data stored in the internal buffer and pro-

gram it into the appropriate OTP Security Register locations based on the starting address

specified by A23-A0 and the number of data bytes sent to the device. If less than 64 bytes of

data were sent to the device, then the remaining bytes within the OTP Security Register will not

be programmed and will remain in the erased state (FFh). The programming of the data bytes is

internally self-timed and should take place in a time of t

.

OTPP

The three address bytes and at least one complete byte of data must be clocked into the device

before the CS pin is deasserted, and the CS pin must be deasserted on even byte boundaries

(multiples of eight bits); otherwise, the device will abort the operation and the user-programma-

ble portion of the OTP Security Register will not be programmed. The WEL bit in the Status

Register will be reset back to the logical “0” state if the OTP Security Register program cycle

aborts due to an incomplete address being sent, an incomplete byte of data being sent, the CS

pin being deasserted on uneven byte boundaries, or because the user-programmable portion of

the OTP Security Register was previously programmed.

While the device is programming the OTP Security Register, the Status Register can be read

and will indicate that the device is busy. For faster throughput, it is recommended that the Status

Register be polled rather than waiting the t

time to determine if the data bytes have finished

OTPP

programming. At some point before the OTP Security Register programming completes, the

WEL bit in the Status Register will be reset back to the logical “0” state.

If the device is powered-down during the OTP Security Register program cycle, then the con-

tents of the 64-byte user programmable portion of the OTP Security Register cannot be

guaranteed and cannot be programmed again.

The Program OTP Security Register command utilizes the internal 256-buffer for processing.

Therefore, the contents of the buffer will be altered from its previous state when this command is

issued.

AT25DF021

20

3677D–DFLASH–04/09