TDA9984AHW/15/C181 NXP Semiconductors, TDA9984AHW/15/C181 Datasheet - Page 28

TDA9984AHW/15/C181

Manufacturer Part Number

TDA9984AHW/15/C181

Description

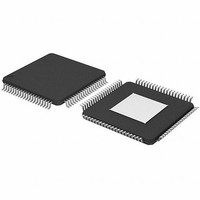

HDMI TRANSMITTER 1080P 80HTQFP

Manufacturer

NXP Semiconductors

Type

HDMI 1.3 Transmitterr

Datasheet

1.TDA9984AHW15C181.pdf

(40 pages)

Specifications of TDA9984AHW/15/C181

Package / Case

80-TQFP Exposed Pad, 80-eTQFP, 80-HTQFP, 80-VQFP

Applications

Set-Top Boxes, Video Players, Recorders

Mounting Type

Surface Mount

Operating Supply Voltage

1.8 V, 3.3 V

Supply Current

6 mA to 283 mA

Bandwidth

150 MHz

Conversion Rate

12 bit

Maximum Power Dissipation

1080 mW

Mounting Style

SMD/SMT

Resolution

12 bit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

935288944518

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

TDA9984AHW/15/C181

Manufacturer:

NXP Semiconductors

Quantity:

10 000

NXP Semiconductors

9. I

TDA9984A_4

Product data sheet

2

C-bus registers definitions

8.7 I

9.1 Memory page management

9.2 ID version

The I

pin. Both Fast-mode (400 kHz) and Standard-mode (100 kHz) are supported. The

registers of the TDA9984A can be accessed via the I

some, which cannot be read for confidentiality.

The TDA9984A is used as a slave I

address are externally selected by pins A0 and A1 (see

Table 18.

The I

Firstly, the master writes the TDA9984A address and the subaddress to access the

specific register, and then the data.

The I

with common register CURPAGE_ADR. It is only necessary to write in this register once

to change the current page. So multiple read or write operations in the same page need a

write register CURPAGE_ADR once at the beginning.

Table 19.

The ID-version readable via I

Device address

A6

1

Page address

00h

01h

02h

09h

10h

11h

12h

2

Fig 16. I

C-bus interface

2

2

2

C-bus pins I2C_SDA and I2C_SCL are 5 V tolerant. Pin I2C_SCL is only an input

C-bus access format is shown in

C-bus memory is split into several pages and the selection between pages is made

2

Device address

Memory pages

C-bus access

A5

1

SDA

SCL

Memory page description

general control

scaler and PLL scaling

PLL settings

EDID control page

InfoFrames and packets

audio settings and content info packets

HDCP and OTP

1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 9

SLAVE ADDRESS

Rev. 04 — 15 January 2009

A4

1

2

C-bus is defined as follows:

HDMI 1.3 transmitter with 1080p upscaler embedded

A3

0

2

C-bus device. Bits A0 and A1 of the I

SUBADDRESS

Figure

A2

0

16.

2

C-bus. All registers are R/W except

Table

A1

pin A1

DATA

18).

TDA9984A

001aaf292

A0

pin A0

STOP

© NXP B.V. 2009. All rights reserved.

2

C-bus device

W/R

-

0/1

28 of 40