TDA9984AHW/15/C181 NXP Semiconductors, TDA9984AHW/15/C181 Datasheet - Page 26

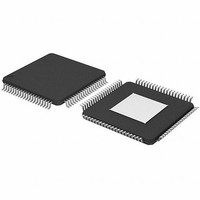

TDA9984AHW/15/C181

Manufacturer Part Number

TDA9984AHW/15/C181

Description

HDMI TRANSMITTER 1080P 80HTQFP

Manufacturer

NXP Semiconductors

Type

HDMI 1.3 Transmitterr

Datasheet

1.TDA9984AHW15C181.pdf

(40 pages)

Specifications of TDA9984AHW/15/C181

Package / Case

80-TQFP Exposed Pad, 80-eTQFP, 80-HTQFP, 80-VQFP

Applications

Set-Top Boxes, Video Players, Recorders

Mounting Type

Surface Mount

Operating Supply Voltage

1.8 V, 3.3 V

Supply Current

6 mA to 283 mA

Bandwidth

150 MHz

Conversion Rate

12 bit

Maximum Power Dissipation

1080 mW

Mounting Style

SMD/SMT

Resolution

12 bit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

935288944518

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

TDA9984AHW/15/C181

Manufacturer:

NXP Semiconductors

Quantity:

10 000

NXP Semiconductors

TDA9984A_4

Product data sheet

8.5.2 Interrupt controller

8.5.3 Hot plug detection

8.5.4 Initialization

Here is described briefly the clock system architecture:

Each PLL can be bypassed via the I

independently to each block.

Pin INT is used to alert the microcontroller that a critical event concerning the HDMI has

occurred. Some of theses interrupts are maskable. See

generated by the TDA9984A.

Table 17.

Pin HPD is the hot plug detect pin; it is 5 V input tolerant. When asserted, the hot plug

detect signal tells the transmitter that the receiver is connected. When changing from

LOW to HIGH, the TDA9984A has to read EDID to match the video format to the format

the receiver can handle.

After power-up, the TDA9984A is activated by a hard reset. Pin RST_N can be used to

activate the TDA9984A in a known state.

The device also offers the possibility to perform a soft reset that will affect a certain

number of I

proper initialization of the device.

Interrupt

Domain

HDCP

HPD

RxSense

EDID

Interrupt

•

•

•

PLL double edge: generates a clock at twice the VCLK input frequency to capture

correctly the data at the video formatter input

PLL scaling: creates a new video processing scaled clock taking into account the

scaling ratio programmed in the scaler

PLL serializer: a system clock generator, which enables the stream produced by the

encoder to be transmitted on the TMDS data channel at ten times or above the

sampling rate; see

Interrupts

2

C-bus registers, but not all of them. This soft reset is also mandatory for a

Interrupt name

r0

pj

sha-1

bstatus

bcaps

t0

security

hpd

rx_sense

edid_block_rd

sw_intsoftware

Rev. 04 — 15 January 2009

Section 8.4.3

HDMI 1.3 transmitter with 1080p upscaler embedded

2

C-bus and then external clock VCLK can be provided

Definition

r0 = R’0 check done

pj = P’j check fails

V = V’ check success

bstatus available

bcaps available

HDCP goes to initial state

HDCP encryption is off or blue

screen removed

transition on HPD input

transition on RxSense

EDID block read finished

test purpose

Table 17

for the interrupt types

TDA9984A

© NXP B.V. 2009. All rights reserved.

Maskable

feature

maskable

not maskable

maskable

26 of 40