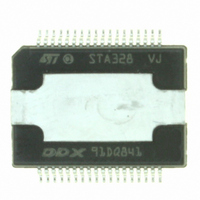

STA32813TR STMicroelectronics, STA32813TR Datasheet - Page 31

STA32813TR

Manufacturer Part Number

STA32813TR

Description

IC DAS 2.1CH HI EFF POWERSO36

Manufacturer

STMicroelectronics

Series

DDX™r

Type

Audio Ampr

Datasheet

1.STA32813TR.pdf

(57 pages)

Specifications of STA32813TR

Mounting Type

Surface Mount

Package / Case

36-PowerSOIC

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Applications

-

Other names

497-8876-2

STA328

6.6

Configuration register F (addr 0x05)

Table 40.

Table 41.

Table 42.

Setting the IDE bit enables this function, which looks at the input I

will automatically mute all outputs if the signals are perceived as invalid.

Table 43.

Detects loss of input MCLK in binary mode and will output 50% duty cycle to prevent audible

artifacts when input clocking is lost.

1:0

00

01

10

11

2

3

Bit

Bit

Bit

EAPD

OCFG[1:0]

D7

0

RW

RW

RW

R/W

R/W

R/W

Output configuration selection

Output configuration selection

Invalid input detect mute enable

Binary clock loss detection enable

PWDN

00

1

1

RST

RST

RST

D6

1

2 channel (full-bridge) power, 1 channel

1A/1B ◊ 1A/1B

2A/2B ◊ 2A/2B

2 (half-bridge) and 1 (full-bridge) on-board power:

1A ◊ 1A binary

2A ◊ 1B binary

3A/3B ◊ 2A/2B binary

Reserved

1 channel mono-parallel:

3A ◊ 1A/1B

3B ◊ 2A/2B

OCFG[1:0]

IDE

BCLE

ECLE

Name

Name

Name

D5

0

Reserved

D4

1

Output configuration selection

00: 2-channel (full-bridge) power, 1-channel

default

Invalid input detect auto-mute enable:

0: disabled

1: enabled

Binary output mode clock loss detection enable

0: disabled

1: enabled

Output power configuration

BCLE

D3

1

DDX

IDE

D2

®

Description

1

Description

Description

:

2

S data and clocking and

OCFG1

Register description

D1

0

DDX

OCFG0

D0

®

0

is

31/57