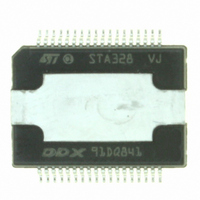

STA32813TR STMicroelectronics, STA32813TR Datasheet - Page 16

STA32813TR

Manufacturer Part Number

STA32813TR

Description

IC DAS 2.1CH HI EFF POWERSO36

Manufacturer

STMicroelectronics

Series

DDX™r

Type

Audio Ampr

Datasheet

1.STA32813TR.pdf

(57 pages)

Specifications of STA32813TR

Mounting Type

Surface Mount

Package / Case

36-PowerSOIC

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Applications

-

Other names

497-8876-2

I

5

5.1

5.2

16/57

2

C bus specification

I

The STA328 supports the I

to the I

that controls the data transfer is known as the master and the other as the slave. The master

always starts the transfer and provides the serial clock for synchronization. The STA328 is

always a slave device in all of its communications.

Communication protocol

Data transition or change

Data changes on the SDA line must only occur when the SCL clock is low. SDA transition

while the clock is high is used to identify a START or STOP condition.

Start condition

START is identified by a high to low transition of the data bus SDA signal while the clock

signal SCL is stable in the high state. A START condition must precede any command for

data transfer.

Stop condition

STOP is identified by a low to high transition of the data bus SDA signal while the clock

signal SCL is stable in the high state. A STOP condition terminates communication between

STA328 and the bus master.

Data input

During the data input the STA328 samples the SDA signal on the rising edge of clock SCL.

For correct device operation the SDA signal must be stable during the rising edge of the

clock and the data can change only when the SCL line is low.

Device addressing

To start communication between the master and the STA328, the master must initiate with a

start condition. Following this, the master sends 8 bits (MSB first) onto the SDA line

corresponding to the device select address and read or write mode.

The 7 MSBs are the device address identifiers, corresponding to the I

STA328 device address is decimal 34 (binary 00100010).

The 8th bit (LSB) identifies read or write operation, RW. This bit is set to 1 in read mode and

0 for write mode. After a START condition the STA328 identifies the device address on the

bus. If a match is found, it acknowledges the identification on the SDA bus during the 9th bit

time. The byte following the device identification byte is the internal space address.

2

C bus specification

2

C bus as a transmitter and any device that reads the data as a receiver. The device

2

C protocol. This protocol defines any device that sends data on

2

C bus definition. The

STA328