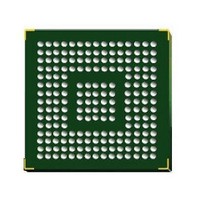

STM32F417IGH6 STMicroelectronics, STM32F417IGH6 Datasheet - Page 24

STM32F417IGH6

Manufacturer Part Number

STM32F417IGH6

Description

Microcontrollers (MCU) ARM M4 1024 FLASH 168 Mhz 192kB SRAM

Manufacturer

STMicroelectronics

Specifications of STM32F417IGH6

Core

ARM Cortex M4

Processor Series

STM32F4

Data Bus Width

32 bit

Maximum Clock Frequency

168 MHz

Program Memory Size

1024 KB

Data Ram Size

192 KB

On-chip Adc

Yes

Number Of Programmable I/os

140

Number Of Timers

10

Operating Supply Voltage

1.7 V to 3.6 V

Package / Case

UFBGA-176

Mounting Style

SMD/SMT

A/d Bit Size

12 bit

A/d Channels Available

24

Interface Type

CAN, I2C, I2S, SPI, UART

Program Memory Type

Flash

Lead Free Status / Rohs Status

Details

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

STM32F417IGH6

Manufacturer:

STMicroelectronics

Quantity:

480

Description

24/156

Regulator OFF

This mode allows to power the device as soon as V

●

●

Regulator OFF/internal reset ON

This mode is available only on UFBGA package. It is activated by setting

BYPASS_REG and PDR_ON pins to V

The regulator OFF/internal reset ON mode allows to supply externally a 1.2 V voltage

source through V

The following conditions must be respected:

–

–

–

In regulator OFF/internal reset ON mode, PA0 cannot be used as a GPIO pin since it

allows to reset the part of the 1.2 V logic which is not reset by the NRST pin, when the

internal voltage regulator in off.

Regulator OFF/internal reset OFF

This mode is available only on UFBGA package. It is activated by setting

BYPASS_REG pin to V

allows to supply externally a 1.2 V voltage source through V

addition to V

The following conditions must be respected:

–

–

–

V

between power domains.

If the time for V

reach 1.8 V

Otherwise, PA0 should be asserted low externally during POR until V

1.8 V (see

If V

must be asserted on PA0 pin.

V

between power domains.

PA0 should be kept low to cover both conditions: until V

1.08 V and until V

NRST should be controlled by an external reset controller to keep the device

under reset when V

DD

DD

CAP_1

should always be higher than V

should always be higher than V

DD

and V

.

Figure

(a)

CAP_1

, then PA0 should be connected to the NRST pin (see

CAP_1

CAP_2

DD

9).

and V

DD

DD

Doc ID 022063 Rev 1

reaches 1.8 V (see

and V

and by applying an inverted reset signal to PDR_ON, and

go below 1.08 V and V

is below 1.8 V (see

CAP_2

CAP_2

pins, in addition to V

to reach 1.08 V is faster than the time for V

DD

CAP_1

CAP_1

.

Figure

DD

and V

and V

Figure

DD

reaches 1.8 V.

8).

is higher than 1.7 V, then a reset

CAP_2

CAP_2

9).

STM32F415xx, STM32F417xx

DD

.

to avoid current injection

to avoid current injection

CAP_1

CAP_1

and V

and V

CAP_2

CAP_2

Figure

DD

reaches

pins, in

reach

8).

DD

to