CYP15G0401DXB-BGC Cypress Semiconductor Corp, CYP15G0401DXB-BGC Datasheet - Page 10

CYP15G0401DXB-BGC

Manufacturer Part Number

CYP15G0401DXB-BGC

Description

IC TXRX HOTLINK 256LBGA

Manufacturer

Cypress Semiconductor Corp

Series

HOTlink II™r

Type

Transceiverr

Datasheet

1.CYW15G0401DXB-BGXC.pdf

(53 pages)

Specifications of CYP15G0401DXB-BGC

Package / Case

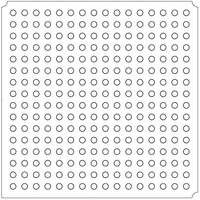

256-LBGA Exposed Pad, 32-HLBGA

Number Of Drivers/receivers

4/4

Protocol

Multiprotocol

Voltage - Supply

3.135 V ~ 3.465 V

Mounting Type

Surface Mount

Product

PHY

Supply Voltage (min)

3.135 V

Supply Current

1.06 A

Maximum Operating Temperature

+ 70 C

Minimum Operating Temperature

0 C

Mounting Style

SMD/SMT

Number Of Channels

4

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

CYP15G0401DX-EVAL - IC TXRX HOTLINK 256-BGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CYP15G0401DXB-BGC

Manufacturer:

CY

Quantity:

767

Company:

Part Number:

CYP15G0401DXB-BGC

Manufacturer:

CYPRESS

Quantity:

586

Company:

Part Number:

CYP15G0401DXB-BGC

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

Part Number:

CYP15G0401DXB-BGC

Manufacturer:

CYPRESS/赛普拉斯

Quantity:

20 000

Document #: 38-02002 Rev. *L

Pin Descriptions

CYP(V)(W)15G0401DXB Quad HOTLink II Transceiver

Transmit Path Mode Control

TXMODE[1:0] Three-level Select

Receive Path Data Signals

RXDA[7:0]

RXDB[7:0]

RXDC[7:0]

RXDD[7:0]

RXSTA[2:0]

RXSTB[2:0]

RXSTC[2:0]

RXSTD[2:0]

RXOPA

RXOPB

RXOPC

RXOPD

Receive Path Clock and Clock Control

RXRATE

FRAMCHAR Three-level Select

RFEN

RXMODE[1:0] Three-level Select

Pin Name

static control inputs

LVTTL Output,

synchronous to the

selected RXCLKx↑ output

(or REFCLK↑ input

when RXCKSEL = LOW)

LVTTL Output,

synchronous to the

selected RXCLKx↑ output

(or REFCLK↑ input

when RXCKSEL = LOW)

three-state, LVTTL

Output, synchronous to

the selected

RXCLKx↑ output

(or REFCLK↑ input

when RXCKSEL = LOW)

LVTTL Input, static control

input, internal pull-down

static control input

LVTTL Input,

asynchronous,

internal pull-down

static control inputs

I/O Characteristics

(continued)

[5]

[5]

[5]

[4]

[4]

[4]

,

,

Transmit Operating Mode. These inputs are interpreted to select one of nine

operating modes of the transmit path. See Table 3 for a list of operating modes.

Parallel Data Output. These outputs change following the rising edge of the selected

receive interface clock.

When the Decoder is enabled (DECMODE = HIGH or MID), these outputs represent

either received data or special characters. The status of the received data is repre-

sented by the values of RXSTx[2:0].

When the Decoder is bypassed (DECMODE = LOW), RXDx[7:0] become the higher

order bits of the 10-bit received character. See Table 18 for details.

Parallel Status Output. These outputs change following the rising edge of the

selected receive interface clock.

When the Decoder is bypassed (DECMODE = LOW), RXSTx[1:0] become the two

low-order bits of the 10-bit received character, while RXSTx[2] = HIGH indicates the

presence of a Comma character in the Output Register. See Table 18 for details.

When the Decoder is enabled (DECMODE = HIGH or MID), RXSTx[2:0] provide

status of the received signal. See Table 20, 23 and 24 for a list of Receive Character

status.

Receive Path Odd Parity. When parity generation is enabled (PARCTL ≠ LOW), the

parity output at these pins is valid for the data on the associated RXDx bus bits. When

parity generation is disabled (PARCTL = LOW) these output drivers are disabled

(High-Z).

Receive Clock Rate Select. When LOW, the RXCLKx± recovered clock outputs are

complementary clocks operating at the recovered character rate. Data for the

associated receive channels should be latched on the rising edge of RXCLKx+ or

falling edge of RXCLKx–.

When HIGH, the RXCLKx± recovered clock outputs are complementary clocks

operating at half the character rate. Data for the associated receive channels should

be latched alternately on the rising edge of RXCLKx+ and RXCLKx–.

When REFCLK± is selected to clock the output registers (RXCKSELx = LOW),

RXRATEx is not interpreted. The RXCLKA± and RXCLKC± output clocks will follow

the frequency and duty cycle of REFCLK±.

Framing Character Select. Used to select the character or portion of a character

used for character framing of the received data streams. When MID, the Framer looks

for both positive and negative disparity versions of the eight-bit Comma character.

When HIGH, the Framer looks for both positive and negative disparity versions of the

K28.5 character. Configuring FRAMCHAR to LOW is reserved for component test.

Reframe Enable for All Channels. Active HIGH. When HIGH, the framers in all four

channels are enabled to frame per the presently enabled framing mode as selected

by RFMODE and selected framing character as selected by FRAMCHAR.

Receive Operating Mode. These inputs are interpreted to select one of nine

operating modes of the receive path. See Table 14 for details.

Signal Description

CYW15G0401DXB

CYP15G0401DXB

CYV15G0401DXB

Page 10 of 53