PCA9564BS,118 NXP Semiconductors, PCA9564BS,118 Datasheet - Page 3

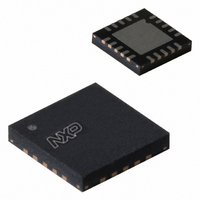

PCA9564BS,118

Manufacturer Part Number

PCA9564BS,118

Description

IC CTRL PARALLEL/I2C BUS 20HVQFN

Manufacturer

NXP Semiconductors

Datasheet

1.PCA9564PW112.pdf

(32 pages)

Specifications of PCA9564BS,118

Package / Case

20-VQFN Exposed Pad, 20-HVQFN, 20-SQFN, 20-DHVQFN

Controller Type

Parallel Bus to I²C Bus Controller

Interface

I²C

Voltage - Supply

2.3 V ~ 3.6 V

Current - Supply

6mA

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Logic Family

PCA

Maximum Operating Temperature

+ 85 C

Minimum Operating Temperature

- 40 C

High Level Output Current

- 7 mA

Low Level Output Current

8.5 mA

Mounting Style

SMD/SMT

Supply Voltage (max)

3.6 V

Supply Voltage (min)

2.3 V

Number Of Circuits

Single

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

568-4001 - DEMO BOARD FOR PCA9564

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

568-3405-2

935272895118

PCA9564BS-T

935272895118

PCA9564BS-T

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

PCA9564BS,118

Manufacturer:

Exar

Quantity:

68

1. HVQFN package die supply ground is connected to both V

Philips Semiconductors

PIN CONFIGURATION — DIP, SO, TSSOP

PIN DESCRIPTION

NOTES:

2006 Sep 01

DIP, SO, TSSOP

Parallel bus to I

proper device operation. For enhanced thermal, electrical, and board level performance, the exposed pad needs to be soldered to the board

using a corresponding thermal pad on the board and for proper heat conduction through the board, thermal vias need to be incorporated in

the PCB in the thermal pad region.

1, 2, 3, 4,

5, 6, 7, 8

14, 15

10

11

12

13

16

17

18

19

20

9

PIN NUMBER

DNU

V

D1

D2

D3

D4

D5

D6

D7

D0

SS

1, 2, 3, 4, 5,

18, 19, 20

HVQFN

10

11, 12

1

2

3

4

5

6

7

8

9

10

13

14

15

16

17

7

6

8

9

1

2

C-bus controller

SW02260

SYMBOL

D0–D7

DNU

V

WR

RD

CE

A0, A1

INT

RESET

SCL

SDA

V

SS

DD

20

19

18

17

16

15

14

13

12

11

V

SDA

SCL

RESET

INT

A1

A0

CE

RD

WR

DD

I/O

Pwr

I

I

I

I

O

I

I/O

I/O

Pwr

TYPE

PIN

PIN

Data Bus: Bi-directional 3-State data bus used to transfer commands, data and

status between the controller and the CPU. D0 is the least significant bit.

Do not use: must be left floating (pulled LOW internally)

Ground

Write Strobe: When LOW and CE is also LOW, the contents of the data bus is

loaded into the addressed register. The transfer occurs on the rising edge of the

signal.

Read Strobe: When LOW and CE is also LOW, causes the contents of the

addressed register to be presented on the data bus. The read cycle begins on the

falling edge of RD.

Chip Enable: Active-LOW input signal. When LOW, data transfers between the CPU

and the controller are enabled on D0–D7 as controlled by the WR, RD and A0–A1

inputs. When HIGH, places the D0–D7 lines in the 3-State condition.

Address Inputs: Selects the controller internal registers and ports for read/write

operations.

Interrupt Request: Active-LOW, open-drain, output. This pin requires a pull-up

device.

Reset: A LOW level clears internal registers resets the I

I

I

Power Supply: 2.3 to 3.6 V

2

2

C-bus serial clock input/output (open-drain).

C-bus serial data input/output (open-drain).

SS

pin and exposed center pad. V

3

PIN CONFIGURATION — HVQFN

NAME AND FUNCTION

D3

D4

D5

D6

D7

1

2

3

4

5

SS

pin must be connected to supply ground for

TOP VIEW

2

C state machine.

15

14

13

12

11

SW02261

RESET

INT

A1

A0

SCL

PCA9564

Product data sheet