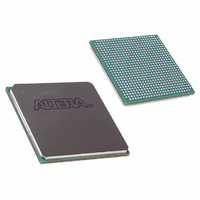

EP2S60F672I4N Altera, EP2S60F672I4N Datasheet - Page 99

EP2S60F672I4N

Manufacturer Part Number

EP2S60F672I4N

Description

IC STRATIX II FPGA 60K 672-FBGA

Manufacturer

Altera

Series

Stratix® IIr

Datasheet

1.EP2S15F484I4N.pdf

(238 pages)

Specifications of EP2S60F672I4N

Number Of Logic Elements/cells

60440

Number Of Labs/clbs

3022

Total Ram Bits

2544192

Number Of I /o

492

Voltage - Supply

1.15 V ~ 1.25 V

Mounting Type

Surface Mount

Operating Temperature

-40°C ~ 100°C

Package / Case

672-FBGA

For Use With

544-1700 - DSP KIT W/STRATIX II EP2S60N544-1697 - NIOS II KIT W/STRATIX II EP2S60N

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Gates

-

Other names

544-1916

EP2S60F672I4N

EP2S60F672I4N

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP2S60F672I4N

Manufacturer:

ALTERA

Quantity:

201

Company:

Part Number:

EP2S60F672I4N

Manufacturer:

ALTERA

Quantity:

400

Part Number:

EP2S60F672I4N

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

Altera Corporation

May 2007

Note to

(1)

Series termination with

calibration

Parallel termination with

calibration

Differential termination

Table 2–17. On-Chip Termination Support by I/O Banks (Part 2 of 2)

On-Chip Termination Support

Clock pins CLK1, CLK3, CLK9, CLK11, and pins FPLL[7..10]CLK do not support differential on-chip

termination. Clock pins CLK0, CLK2, CLK8, and CLK10 do support differential on-chip termination. Clock pins in

the top and bottom banks (CLK[4..7, 12..15]) do not support differential on-chip termination.

Table

2–17:

(1)

3.3-V LVTTL

3.3-V LVCMOS

2.5-V LVTTL

2.5-V LVCMOS

1.8-V LVTTL

1.8-V LVCMOS

1.5-V LVTTL

1.5-V LVCMOS

SSTL-2 Class I and II

SSTL-18 Class I and II

1.8-V HSTL Class I

1.8-V HSTL Class II

1.5-V HSTL Class I

1.2-V HSTL

SSTL-2 Class I and II

SSTL-18 Class I and II

1.8-V HSTL Class I

1.8-V HSTL Class II

1.5-V HSTL Class I and II

1.2-V HSTL

LVDS

HyperTransport technology

I/O Standard Support

Top & Bottom Banks

Stratix II Device Handbook, Volume 1

v

v

v

v

v

v

v

v

v

v

v

v

v

v

v

v

v

v

v

v

Stratix II Architecture

Left & Right Banks

v

v

2–91