EP2S60F672I4N Altera, EP2S60F672I4N Datasheet - Page 157

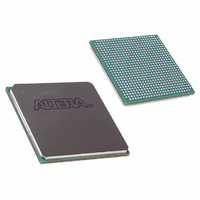

EP2S60F672I4N

Manufacturer Part Number

EP2S60F672I4N

Description

IC STRATIX II FPGA 60K 672-FBGA

Manufacturer

Altera

Series

Stratix® IIr

Datasheet

1.EP2S15F484I4N.pdf

(238 pages)

Specifications of EP2S60F672I4N

Number Of Logic Elements/cells

60440

Number Of Labs/clbs

3022

Total Ram Bits

2544192

Number Of I /o

492

Voltage - Supply

1.15 V ~ 1.25 V

Mounting Type

Surface Mount

Operating Temperature

-40°C ~ 100°C

Package / Case

672-FBGA

For Use With

544-1700 - DSP KIT W/STRATIX II EP2S60N544-1697 - NIOS II KIT W/STRATIX II EP2S60N

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Gates

-

Other names

544-1916

EP2S60F672I4N

EP2S60F672I4N

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP2S60F672I4N

Manufacturer:

ALTERA

Quantity:

201

Company:

Part Number:

EP2S60F672I4N

Manufacturer:

ALTERA

Quantity:

400

Part Number:

EP2S60F672I4N

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

Altera Corporation

April 2011

Preliminary status means the timing model is subject to change. Initially,

timing numbers are created using simulation results, process data, and

other known parameters. These tests are used to make the preliminary

numbers as close to the actual timing parameters as possible.

Final timing numbers are based on actual device operation and testing.

These numbers reflect the actual performance of the device under

worst-case voltage and junction temperature conditions.

I/O Timing Measurement Methodology

Altera characterizes timing delays at the worst-case process, minimum

voltage, and maximum temperature for input register setup time (t

and hold time (t

to calculate t

Figure 5–3

Table 5–33. Stratix II Device Timing Model Status

t

t

SU

H

= – data delay from input pin to input register

EP2S130

EP2S180

= + data delay from input pin to input register

EP2S15

EP2S30

EP2S60

EP2S90

Device

+ micro setup time of the input register

– clock delay from input pin to input register

+ micro hold time of the input register

+ clock delay from input pin to input register

shows the setup and hold timing diagram for input registers.

SU

and t

H

). The Quartus II software uses the following equations

H

timing for Stratix II devices input signals.

Preliminary

Stratix II Device Handbook, Volume 1

DC & Switching Characteristics

Final

v

v

v

v

v

v

SU

5–21

)