ISL1208IU8Z Intersil, ISL1208IU8Z Datasheet

ISL1208IU8Z

Specifications of ISL1208IU8Z

Available stocks

Related parts for ISL1208IU8Z

ISL1208IU8Z Summary of contents

Page 1

... CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures. 1-888-INTERSIL or 1-888-468-3774 All other trademarks mentioned are the property of their respective owners. ISL1208 2 ® Real Time Clock/Calendar FN8085.8 | Intersil (and design registered trademark of Intersil Americas Inc. Copyright Intersil Americas Inc. 2004-2006, 2008. All Rights Reserved ...

Page 2

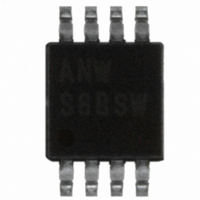

... Ordering Information PART NUMBER PART MARKING ISL1208IU8 AGS ISL1208IU8-TK* AGS ISL1208IU8Z (Note) ANW ISL1208IU8Z-TK* ANW (Note) ISL1208IB8 1208 I ISL1208IB8-TK* 1208 I ISL1208IB8Z 1208 ZI (Note) ISL1208IB8Z-TK* 1208 ZI (Note) ISL1208IRT8Z 08TZ (Note) ISL1208IRT8Z-TK* 08TZ (Note) *Please refer to TB347 for details on reel specifications. NOTE: These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations) ...

Page 3

Pin Descriptions PIN NUMBER SYMBOL 1 X1 The X1 pin is the input of an inverting amplifier and is intended to be connected to one pin of an external 32.768kHz quartz crystal. X1 can also be driven directly from a ...

Page 4

... Thermal Information Thermal Resistance (Typical, Note 1) SOIC Package . . . . . . . . . . . . . . . . . . . MSOP Package . . . . . . . . . . . . . . . . . . + 0.5 (V Mode) TDFN Package (Note 2 0.5 (V Mode) Storage Temperature . . . . . . . . . . . . . . . . . . . . . . . .-65°C to +150°C BAT BAT Pb-free Reflow Profile . . . . . . . . . . . . . . . . . . . . . . . . .see link below http://www.intersil.com/pbfree/Pb-FreeReflow.asp BAT Temperature = -40°C to +85°C, unless otherwise stated. CONDITIONS Active ...

Page 5

Serial Interface Specifications SYMBOL PARAMETER V SDA and SCL Input Buffer HIGH IH Voltage Hysteresis SDA and SCL Input Buffer Hysteresis V SDA Output Buffer LOW Voltage, OL Sinking 3mA C SDA and SCL Pin Capacitance PIN f SCL Frequency ...

Page 6

SDA vs SCL Timing SCL t SU:STA t HD:STA SDA (INPUT TIMING) SDA (OUTPUT TIMING) Symbol Table WAVEFORM INPUTS Must be steady May change from LOW to HIGH May change from HIGH to LOW Don’t Care: Changes Allowed N/A 6 ...

Page 7

Typical Performance Curves 1E-6 900E-9 800E-9 700E-9 600E-9 500E-9 400E-9 300E-9 200E-9 100E-9 000E+0 1.5 2.0 2.5 3.0 3.5 V (V) BAT FIGURE BAT 2.4E-06 2.2E- 2.0E-06 1.8E-06 1.6E- ...

Page 8

... VDD pin to ground. Functional Description Power Control Operation The power control circuit accepts a V Many types of batteries can be used with Intersil RTC products. For example, 3.0V or 3.6V Lithium batteries are appropriate, and battery sizes are available that can power X1 ...

Page 9

ISL1208 for years. Another option is to use a Super Cap for applications where month. See the “Application Section” on page 18 for more information. Normal Mode ( Battery Backup ...

Page 10

Accuracy of the Real Time Clock The accuracy of the Real Time Clock depends on the frequency of the quartz crystal that is used as the time base for the RTC. Since the resonant frequency of a crystal is temperature ...

Page 11

Write capability is allowable into the RTC registers (00h to 06h) only when the WRTC bit (bit 4 of address 07h) is set to “1”. A multi-byte read or write operation is limited to one section per operation. Access to ...

Page 12

Real Time Clock Registers Addresses [00h to 06h] RTC REGISTERS (SC, MN, HR, DT, MO, YR, DW) These registers depict BCD representations of the time. As such, SC (Seconds) and MN (Minutes) range from 0 to 59, HR (Hour) can ...

Page 13

FREQUENCY OUT CONTROL BITS (FO <3:0>) These bits enable/disable the frequency output function and select the output frequency at the IRQ/fOUT pin. See Table 4 for frequency selection. When the frequency mode is enabled, it will override the alarm mode ...

Page 14

The effective series load capacitance is the combination of C and C in Equation 2 ---------------------------------- - C = LOAD ⎛ ⎞ ---------- - + ---------- - ⎝ ⎠ ⋅ ⋅ ...

Page 15

Below are examples of both Single Event and periodic Interrupt Mode alarms. Example 1 – Alarm set with single interrupt (IM=”0”) A single alarm will occur on January 1 at 11:30am. A. Set Alarm registers as follows: BIT ALARM REGISTER ...

Page 16

SDA line LOW to acknowledge the reception of the eight bits of data (See Figure 13). The ISL1208 responds with an ACK after recognition of a START condition followed by a valid Identification Byte, and once again ...

Page 17

Device Addressing Following a start condition, the master must output a Slave Address Byte. The 7 MSBs are the device identifier. These bits are “1101111”. Slave bits “1101” access the register. Slave bits “111” specify the device select bits. The ...

Page 18

Application Section Oscillator Crystal Requirements The ISL1208 uses a standard 32.768kHz crystal. Either through hole or surface mount crystals can be used. Table 6 lists some recommended surface mount crystals and the parameters of each. This list is not exhaustive ...

Page 19

A system to implement temperature compensation would consist of the ISL1208, a temperature sensor, and a microcontroller. These devices may already be in the system so the function will just be a matter of implementing software and performing some calculations. ...

Page 20

Another consideration is systems with either ground bounce or power supply transients that cause the V below ground for more than a few nanoseconds. This type of power glitch can override the V backup and reset or BAT corrupt the ...

Page 21

Combining with Equation 5 gives the equation for backup time in Equation BACKUP BAT BAT2 BAT1 seconds where 0.47F BAT V = 4.7V BAT2 V = 1.8V ...

Page 22

... Dimensions D2 and E2 are for the exposed pads which provide 5 improved electrical and thermal performance 0. Nominal dimensions are provided to assist with PCB Land Pattern Design efforts, see Intersil Technical Brief TB389. 9. Compliant to JEDEC MO-WEEC-2 except for the “L” min dimension MILLIMETERS MIN ...

Page 23

Small Outline Package Family (SO PIN #1 I.D. MARK 0.010 SEATING PLANE 0.004 C 0.010 MDP0027 SMALL OUTLINE PACKAGE FAMILY (SO) SYMBOL SO-8 SO-14 ...

Page 24

... Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use ...