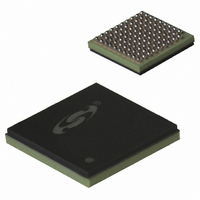

SI5364-F-BC Silicon Laboratories Inc, SI5364-F-BC Datasheet - Page 32

SI5364-F-BC

Manufacturer Part Number

SI5364-F-BC

Description

IC PREC PORT CARD CLOCK 99CBGA

Manufacturer

Silicon Laboratories Inc

Type

Clock Generatorr

Datasheet

1.SI5364-F-BC.pdf

(40 pages)

Specifications of SI5364-F-BC

Package / Case

99-CBGA

Pll

Yes

Input

Clock

Output

CML

Number Of Circuits

1

Ratio - Input:output

3:4

Differential - Input:output

Yes/Yes

Frequency - Max

675MHz

Divider/multiplier

No/Yes

Voltage - Supply

3.135 V ~ 3.465 V

Operating Temperature

-20°C ~ 85°C

Mounting Type

Surface Mount

Frequency-max

675MHz

Mounting Style

SMD/SMT

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Other names

336-1145

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

SI5364-F-BC

Manufacturer:

Silicon Laboratories Inc

Quantity:

10 000

Si5364

32

*Note: The LVTTL inputs on the Si5364 device have an internal pulldown mechanism that causes the input to default to a logic

C7–9, D1–2,

B6–8, C6

Pin #

F1–2

B10

H1

H2

A3

B3

A2

B2

low state if the input is not driven from an external source.

DSBLFSYNC

CAL_ACTV

Rsvd_GND

BWSEL[0]

BWSEL[1]

Pin Name

Rsvd_NC

SYNCIN

FEC[0]

FEC[1]

Table 10. Pin Descriptions (Continued)

I/O

—

—

O

I*

I*

I*

I*

Signal Level

LVTTL

LVTTL

LVTTL

LVTTL

LVTTL

LVTTL

LVTTL

Rev. 2.2

Synchronization Input for Frame Sync Clock.

Allows time alignment/realignment of the FSYNC

output clock. A rising edge on the SYNCIN input

forces alignment of the FSYNC output clock stream.

Disable the FSYNC Clock Output.

When high, the output driver for the FSYNC pin is

disabled.

Forward Error Correction (FEC) Selection.

Enable or disable scaling of the input-to-output fre-

quency multiplication factor for FEC clock rate com-

patibility.

The multiplication ratios and associated frequency

ranges for the Si5364 clock outputs are set by the

FRQSEL pins associated with each clock output.

Additional scaling by a factor of either 255/238 or

238/255 can be applied to all active outputs as indi-

cated below.

The FEC[1:0] inputs are decoded as follows:

00 = No FEC scaling, FSYNC enabled.

01 = 255/238 FEC scaling for all clock outputs,

10 = 238/255 FEC scaling for all clock inputs,

11 = Reserved.

The FSYNC output is disabled when FEC[1:0] = 01.

Bandwidth Select.

The BWSEL[1:0] pins set the bandwidth of the loop

filter within the DSPLL to 3200 Hz, 800 Hz, or

6400 Hz as indicated below.

00 = 3200 Hz

01 = 1600 Hz

10 = 800 Hz

11 = 6400 Hz

Calibration Mode Active.

Is driven high during the DSPLL self-calibration and

the subsequent initial lock acquisition period.

Reserved—Tie to Ground.

Must be tied to GND for normal operation.

Reserved—No Connect.

Must be left unconnected for normal operation.

FSYNC disabled.

FSYNC enabled.

Description