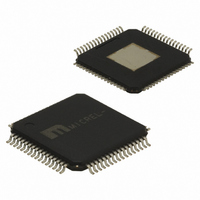

SY89828LHY Micrel Inc, SY89828LHY Datasheet - Page 8

SY89828LHY

Manufacturer Part Number

SY89828LHY

Description

IC BUFFER/XLATOR LVDS 64-TQFP

Manufacturer

Micrel Inc

Series

Precision Edge®r

Type

Fanout Buffer (Distribution), Multiplexer , Translatorr

Datasheet

1.SY89828LHY.pdf

(13 pages)

Specifications of SY89828LHY

Number Of Circuits

2

Ratio - Input:output

2:10

Differential - Input:output

Yes/Yes

Input

LVDS, PECL

Output

LVDS

Frequency - Max

1GHz

Voltage - Supply

3 V ~ 3.6 V

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

64-TQFP Exposed Pad, 64-eTQFP, 64-HTQFP, 64-VQFP

Frequency-max

1GHz

Number Of Clock Inputs

4

Mode Of Operation

Differential

Output Frequency

1000MHz

Output Logic Level

LVDS

Operating Supply Voltage (min)

3V

Operating Supply Voltage (typ)

3.3V

Operating Supply Voltage (max)

3.6V

Package Type

TQFP EP

Operating Temp Range

-40C to 85C

Operating Temperature Classification

Industrial

Signal Type

LVDS/LVPECL

Mounting

Surface Mount

Pin Count

64

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

576-2091

SY89828LHY

SY89828LHY

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

SY89828LHY

Manufacturer:

MICREL

Quantity:

506

Micrel, Inc.

V

Symbol

f

t

t

t

t

t

t

t

t

Note 1.

Note 2.

Note 3.

Note 4.

Note 5.

Note 6.

Note 7.

Note 8.

M9999-012208

hbwhelp@micrel.com or (408) 955-1690

MAX

PHL

PLH

SWITCHOVER

S(OE)

H(OE)

SKEW

JITTER

r

, t

CC

AC ELECTRICAL CHARACTERISTICS

f

= 3.3V ±10%, T

100Ω termination between Q and /Q outputs. Airflow ≥300lfpm, or exposed pad soldered to ground plane.

f

Differential propagation delay is defined as the delay from the crossing point of the differential input signals to the crossing point of the differential

output signals.

Set-up and hold time applies to synchronous applications that intend to enable/disable before the next clock cycle. For asynchronous applications,

set-up and hold time does not apply. OE set-up time is defined with respect to the rising edge of the clock. OE HIGH to LOW transition ensures

outputs remain disabled during the next clock cycle. OE LOW to HIGH transition enables normal operation of the next input clock.

The within-device skew is defined as the worst case difference between any two similar delay paths within a single device identical input transition,

operating at the same voltage and temperature.

The part-to-part skew is defined as the absolute worst case difference between any two delay paths on any two devices operating at the same voltage

and temperature. Part-to-part skew is the total skew difference; pin-to-pin skew + part-to-part skew.

Cycle-to-cycle jitter definition: The variation period between adjacent cycles over a random sample of adjacent cycle pairs. T

where T is the time between rising edges of the output signal.

Total jitter definition: with an ideal clock input, no more than one output edge in 10

to-peak jitter value.

MAX

is defined as the maximum toggle frequency, measured with a 750mV LVPECL input or 350mV LVDS input. Outut swing is > 200mV.

Parameter

Maximum Toggle Frequency

Differential Propagation Delay

Note 3

Clock Input Switchover

Output Enable Set-Up Time

Output Enable Hold Time

Within Device Skew

Part-to-Part Skew

Cycle-to-Cycle

Total Jitter

Output Rise/Fall Times

(20% to 80%)

A

= –40°C to +85°C, unless noted.

Condition

Note 2

LVPECL Input: 150mV

LVPECL Input: 800mV

LVDS Input: 100mV

LVDS Input: 400mV

CLK_SEL to Valid Output

Note 4

Note 4

Note 5

Note 6

Note 7

Note 8

(NOTE 1)

8

12

output edges will deviate by more than the specified peak-

0°C to +85°C

–40°C

0.950

0.950

0.80

1.10

Min

200

1.0

1.0

0.5

1.15

1.35

1.20

1.55

Typ

290

1.0

25

35

<1

JITTER_CC

Precision Edge

1.450

Max

1.45

1.60

1.85

400

400

1.3

50

75

<1

2

SY89828L

= Tn –Tn+1

ps

Units

GHz

ps

ns

ns

ns

ns

ns

ns

ns

ps

ps

ps

ps

RMS

PP

®