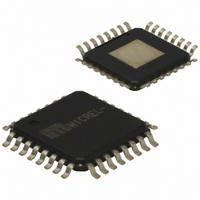

SY69753LHI TR Micrel Inc, SY69753LHI TR Datasheet - Page 3

SY69753LHI TR

Manufacturer Part Number

SY69753LHI TR

Description

IC CLOCK/DATA RECVRY 3.3V 32TQFP

Manufacturer

Micrel Inc

Type

Clock and Data Recovery (CDR)r

Datasheet

1.SY69753LHG.pdf

(13 pages)

Specifications of SY69753LHI TR

Input

PECL, TTL

Output

PECL, TTL

Frequency - Max

1.25GHz

Voltage - Supply

3.15 V ~ 3.45 V

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

32-TQFP Exposed Pad, 32-eTQFP, 32-HTQFP, 32-VQFP

Frequency-max

1.25GHz

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Other names

SY69753LHITR

SY69753LHITR

SY69753LHITR

Pin Description

Inputs

Outputs

Power and Ground

Note:

1. VCC, VCCA, VCCO must be the same value.

December 2007

Pin Number

Pin Number

Pin Number

1, 4, 6, 7, 8

27, 28

29, 30

19, 22

12, 13

26

32

25

16

31

23

24

20

21

18

17

10

14

15

11

2

3

5

9

Pin Name

Pin Name

Pin Name

RDOUTN

RDOUTP

DIVSEL1

DIVSEL2

REFCLK

CLKSEL

RCLKN

RCLKP

TCLKP

TCLKN

PLLRN

RDINP

RDINN

PLLSP

PLLSN

PLLRP

VCCO

GNDA

VCCA

GND

LFIN

VCC

CD

NC

Differential

Differential

Differential

Differential

TTL Input

TTL Input

TTL Input

Output

PECL

PECL

PECL

PECL

PECL

Type

Type

Type

Input

TTL

Pin Name

Serial Data Input: These built-in line receiver inputs are connected to the differential

receive serial data stream. An internal receive PLL recovers the embedded clock

(RCLK) and data (RDOUT) information.

Reference Clock: This input is used as the reference for the internal frequency

synthesizer and the "training" frequency for the receiver PLL to keep it centered in the

absence of data coming in on the RDIN inputs.

Carrier Detect: This input controls the recovery function of the Receive PLL and can be

driven by the carrier detect output of optical modules or from external transition

detection circuitry. When this input is HIGH, the input data stream (RDIN) is recovered

normally by the Receive PLL. When this input is LOW the data on the inputs RDIN will

be internally forced to a constant LOW, the data outputs RDOUT will remain LOW, the

Link Fault Indicator output LFIN forced LOW and the clock recovery PLL forced to look

onto the clock frequency generated from REFCLK.

Divider Select: These inputs select the ratio between the output clock frequency

(RCLK/TCLK) and the REFCLK input frequency as shown in the “Reference Frequency

Selection” table.

Clock Select: This input is used to select either the recovered clock of the receiver PLL

(CLKSEL = HIGH) or the clock of the frequency synthesizer (CLKSEL = LOW) to the

TCLK outputs.

Pin Name

Link Fault Indicator: This output indicates the status of the input data stream RDIN.

Active HIGH signal is indicating when the internal clock recovery PLL has locked onto

the incoming data stream. LFIN will go HIGH if CD is HIGH and RDIN is within the

frequency range of the Receive PLL (1000ppm) and will be alternating if not. LFIN is an

asynchronous output.

Receive Data Output: These ECL 100K outputs represent the recovered data from the

input data stream (RDIN). This recovered data is specified against the rising edge of

RCLK.

Clock Output: These ECL 100K outputs represent the recovered clock used to sample

the recovered data (RDOUT).

Clock Output: These ECL 100K outputs represent either the recovered clock (CLKSEL

= HIGH) used to sample the recovered data (RDOUT) or the transmit clock of the

frequency synthesizer (CLKSEL = LOW).

Clock Synthesis PLL Loop Filter: External loop filter pins for the clock synthesis PLL.

Clock Recovery PLL Loop Filter: External loop filter pins for the receiver PLL.

Pin Name

Power Supply.

Analog Power Supply Voltage.

Output Supply Voltage.

Ground.

No connect.

Analog Ground.

(1)

(1)

3

(1)

hbwhelp@micrel.com

or (408) 955-1690

M9999-120307-F