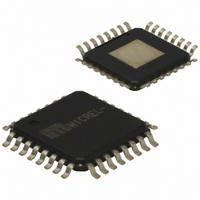

SY87739LHG Micrel Inc, SY87739LHG Datasheet - Page 5

SY87739LHG

Manufacturer Part Number

SY87739LHG

Description

IC SYNTHESIZER FRACT 3.3V 32TQFP

Manufacturer

Micrel Inc

Type

Fractional Synthesizerr

Datasheet

1.SY87739LHY.pdf

(13 pages)

Specifications of SY87739LHG

Input

PECL

Output

PECL

Frequency - Max

729MHz

Voltage - Supply

3.15 V ~ 3.45 V

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

32-TQFP Exposed Pad, 32-eTQFP, 32-HTQFP, 32-VQFP

Frequency-max

729MHz

For Use With

576-1406 - BOARD EVAL N SY87739 EXPERIMENT

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

576-1407

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Micrel, Inc.

General

used in serial data streaming applications, where the

incoming data rate on a channel may vary, or where the

incoming data rate on a channel is unknown ahead of time.

generated even in the absence of any edges on the

corresponding input stream. Up until now, designers had to

resort to sub-optimal solutions such as providing multiple

reference oscillators. Beyond the potential noise and EMI

issues, the designer has no way to future proof his circuit,

as it would prove near impossible to pre-provision all the

reference frequencies that might be needed after

deployment, yet are unknown at this time.

frequencies for common data streaming protocols, all from

one 27MHz reference. If any of these protocols include

overhead due to use of common digital wrappers, The

SY87739L still generates the exact frequency required,

including the overhead.

directly, the SY87739L also generates reference frequencies

for Micrel’s SY87721L CDR/CMU, such that it will reliably

recover data at any rate between 28Mbps and 2,700Mbps

without any gaps.

configuration that describes the desired output reference

frequency. All common microcontrollers support this

MicroWire™ interface. Those microcontrollers that don’t

support this interface in hardware can easily emulate the

interface in firmware.

generates, are divided into three classes. First, the sets of

frequencies that match a particular data streaming protocol

are in the “protocol” category. Second, the set of frequencies

that are guaranteed to be near enough to any arbitrary data

rate such that the SY87721L will lock are in the “picket

fence” category. Third, the set of frequencies that do not fit

into either of the first two categories is in the third category,

frequencies through two tandem PLL circuits. The first PLL

uses a modified fractional-N approach to generate a rational

ratio frequency. This PLL is capable of generating all protocol

data rates, except for those that include FEC or digital

wrapper overhead. A second, more traditional P/Q

synthesizer optionally adjusts the output frequency of the

first, fractional-N synthesizer, to accommodate these FEC

or digital wrapper data rates.

data from a microcontroller to SY87739L. This simple

interface consists of an active high chip select, a serial

clock (2MHz or less) and a serial data input. Each clock

cycle one bit of configuration data transfers to SY87739L.

M9999-062807

hbwhelp@micrel.com or (408) 955-1690

FUNCTIONAL DESCRIPTION

The SY87739L AnyClock™ Fractional-N Synthesizer is

In these situations, a valid output stream must still be

The SY87739L solves this problem by generating exact

Besides generating reference rates for common protocols

A simple 3-wire MicroWire™ bit-serial interface loads a

The large set of possible frequencies that the SY87739L

The SY87739L generates these important reference

The bit serial interface conveys 32 bits of configuration

5

Circuit Description

shown in Figure 1.

one count. That is, if one divider is set to divide by P = 5,

then the other divider divides by P–1 = 4 . The mux choses

between the two based on the control circuit.

input reference edge is used. Only those output edges that

are nearest to an input edge get fed back to the phase-

frequency comparator. In addition, the nearest output edges

are chosen in such a way that the net offset, over a number

of edges, zeroes out. It is the control circuit’s job to drive

the mux such that only the “correct” edges get fed back.

should be, for example, 5 times the input frequency, then P

is set to 5, and the control circuit sets the mux to only feed

back the output of the P divider.

the input frequency, then the control circuit alternates evenly

between the P and the P–1 divider output. For every two

input edges (one to compare against P, and another to

compare against P–1), you will get 5 + 4 output edges,

yielding an output frequency 9/2 the input frequency.

from input to output frequency, the control circuit determines

the fractional part. By mixing the output of the P and P–1

dividers correctly, the control circuit can fashion any output

frequency from P–1 times the input to P times the input, as

long as that ratio can be expressed as a ratio of integers.

The heart of SY87739L is its fractional-N synthesizer, as

The two dividers in the feedback path always differ by

The idea behind the fractional-N approach is that every

In the above fractional-N circuit, if the output frequency

If the output frequency should be, for example, 4

Whereas P sets the integer part of the multiplication factor

Frequency

Reference

Figure 1. Fractional-N Synthesizer Architecture

(f

Input

REF

)

Frequency

Detector/

Phase-

Charge

Pump

Control

Mux

Loop Filter

P-1

P

VCO

Output

Frequency

(f

FNOUT

SY87739L

1

)

/

2

times