LFEC10E-3F484C LATTICE SEMICONDUCTOR, LFEC10E-3F484C Datasheet - Page 51

LFEC10E-3F484C

Manufacturer Part Number

LFEC10E-3F484C

Description

FPGA LatticeEC Family 10200 Cells 340MHz 130nm (CMOS) Technology 1.2V 484-Pin FBGA

Manufacturer

LATTICE SEMICONDUCTOR

Datasheet

1.LFEC3E-5TN144C.pdf

(163 pages)

Specifications of LFEC10E-3F484C

Package

484FBGA

Family Name

LatticeEC

Device Logic Units

10200

Maximum Internal Frequency

340 MHz

Typical Operating Supply Voltage

1.2 V

Maximum Number Of User I/os

288

Ram Bits

282624

In System Programmability

Yes

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

LFEC10E-3F484C

Manufacturer:

Lattice Semiconductor Corporation

Quantity:

10 000

- Current page: 51 of 163

- Download datasheet (962Kb)

Lattice Semiconductor

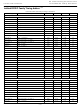

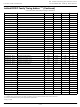

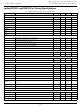

LatticeECP/EC External Switching Characteristics (Continued)

Figure 3-5. DDR Timings

t

t

f

Primary and Secondary Clock

f

t

t

1. General timing numbers based on LVCMOS2.5V, 12 mA. Loading of 0 pF.

2. Using LVDS I/O standard.

3. DDR timing numbers based on SSTL I/O.

4. DDR specifications are characterized but not tested.

5. UI is average bit period.

6. Based on a single primary clock.

7. These timing numbers were generated using ispLEVER design tool. Exact performance may vary with design and tool version. The tool

Timing v.G 0.30

DQVBS

DQVAS

MAX_DDR

MAX_PRI

W_PRI

SKEW_PRI

Parameter

uses internal parameters that have been characterized but are not tested on every device.

2

Data Valid Before DQS

Data Valid After DQS

DDR Clock Frequency

Frequency for Primary Clock Tree

Clock Pulse Width for Primary

Clock

Primary Clock Skew within an I/O

Bank

Description

DQ and DQS Read Timings

DQS

DQ

DQ and DQS Write Timings

DQS

DQ

6

Over Recommended Operating Conditions

All

All

All

All

All

All

Device

t

DQVBS

t

DVADQ

3-15

t

DVEDQ

Min.

0.20

0.20

1.19

t

DQVAS

95

—

—

-5

Max.

200

420

250

—

—

—

DC and Switching Characteristics

LatticeECP/EC Family Data Sheet

Min.

0.20

0.20

1.19

95

—

—

-4

Max.

166

378

300

—

—

—

Min.

0.20

0.20

1.19

95

—

—

-3

Max.

133

340

350

—

—

—

Units

MHz

MHz

UI

UI

ns

ps

Related parts for LFEC10E-3F484C

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

FPGA LatticeEC Family 10200 Cells 340MHz 130nm (CMOS) Technology 1.2V 484-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

FPGA LatticeEC Family 10200 Cells 340MHz 130nm (CMOS) Technology 1.2V 256-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

FPGA LatticeEC Family 10200 Cells 420MHz 130nm (CMOS) Technology 1.2V 484-Pin FBGA

Manufacturer:

LATTICE SEMICONDUCTOR

Datasheet:

Part Number:

Description:

Latticeecp/ec Family of Fpga Devices Has Been Optimized to Deliver Mainstream Fpga Features at Low Cost.for Maximum Performance And Value, The Latticeecp (EConomy Plus) Fpga Concept Combines an Efficient Fpgafabric With High-speed Dedicated Functions

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

ISPLSI2032-80LT44Lattice Semiconductor [In-System Programmable High Density PLD]

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

IC PROGRAMMED LATTICE GAL 16V8

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet:

Part Number:

Description:

357-036-542-201 CARDEDGE 36POS DL .156 BLK LOPRO

Manufacturer:

Lattice Semiconductor Corp.

Datasheet: