S29JL032H90TAI210 Spansion Inc., S29JL032H90TAI210 Datasheet

S29JL032H90TAI210

Specifications of S29JL032H90TAI210

Related parts for S29JL032H90TAI210

S29JL032H90TAI210 Summary of contents

Page 1

... S29JL032H 32 Megabit ( 8-Bit 16-Bit) CMOS 3.0 Volt-only, Simultaneous Read/Write Flash Memory Data Sheet Notice to Readers: This document states the current technical specifications regarding the Spansion product(s) described herein. Each product described herein may be designated as Advance Information, Preliminary, or Full Production. See Publication Number S29JL032H_00 ...

Page 2

... Spansion Inc. The information is intended to help you evaluate this product. Do not design in this product without contacting the factory. Spansion Inc. reserves the right to change or discontinue work on this proposed product without notice.” ...

Page 3

... MHz General Description The S29JL032H megabit, 3.0 volt-only flash memory device, organized as 2,097,152 words of 16 bits each or 4,194,304 bytes of 8 bits each. Word mode data appears on DQ15–DQ0; byte mode data appears on DQ7–DQ0. The device is designed to be programmed in-system with the standard 3.0 volt V and can also be programmed in standard EPROM programmers ...

Page 4

... Autoselect Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 8.10 Sector/Sector Block Protection and Unprotection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22 8.11 Write Protect (WP 8.12 Temporary Sector Unprotect . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24 8.13 Secured Silicon Sector Flash Memory Region . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26 8.14 Hardware Data Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27 9. Common Flash Memory Interface (CFI 10. Command Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31 10.1 Reading Array Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31 10.2 Reset Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31 10 ...

Page 5

Key To Switching Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 6

Figures Figure 8.1 Temporary Sector Unprotect Operation ...

Page 7

Tables Table 8.1 S29JL032H Device Bus Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 8

... The Secured Silicon Customer Indicator Bit (DQ6) is permanently set the part has been locked and lockable. Customers may utilize the Secured Silicon Sector as bonus space, reading and writing like any other flash sector, or may permanently lock their own code there. ...

Page 9

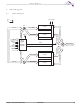

Block Diagram 3.1 4 Bank Device Mux A20–A0 RY/BY# A20–A0 STATE RESET# CONTROL WE# & COMMAND CE# REGISTER BYTE# WP#/ACC DQ0–DQ15 A20–A0 Mux August 31, 2009 S29JL032H_00_B8 ...

Page 10

Bank Device A20–A0 RY/BY# A20–A0 RESET# STATE CONTROL WE# & CE# COMMAND BYTE# REGISTER WP#/ACC DQ15–DQ0 A20–A0 4. Connection Diagrams A15 A14 A13 A12 A11 A10 A19 A20 WE# RESET# WP#/ACC RY/BY# A18 A17 ...

Page 11

Pin Description A20–A0 DQ14–DQ0 DQ15/A-1 CE# OE# WE# WP#/ACC RESET# BYTE# RY/BY Logic Symbol August 31, 2009 S29JL032H_00_B8 Addresses 15 Data Inputs/Outputs (x16-only ...

Page 12

... Ordering Information The order number (Valid Combination) is formed by the following: S29JL032H 60 Device Family S29JL032H 3.0 Volt-only, 32 Megabit ( 16-Bit 8-Bit) Simultaneous Read/Write Flash Memory Manufactured on 130 nm process technology Device Family Speed Option S29JL032H Note 1. Type 0 is standard. Specify others as required; TSOPs can be packed in Types 0 and 3. ...

Page 13

Device Bus Operations This section describes the requirements and use of the device bus operations, which are initiated through the internal command register. The command register itself does not occupy any addressable memory location. The register is a latch ...

Page 14

Requirements for Reading Array Data To read array data from the outputs, the system must drive the CE# and OE# pins to V control and selects the device. OE# is the output control and gates array data to the ...

Page 15

... CMOS standby current (I will be greater. The RESET# pin may be tied to the system reset circuitry. A system reset would thus also reset the Flash memory, enabling the system to read the boot-up firmware from the Flash memory. If RESET# is asserted during a program or erase operation, the RY/BY# pin remains a “0” (busy) until the internal reset operation is complete, which requires a time of t system can thus monitor RY/BY# to determine whether the reset operation is complete ...

Page 16

Output Disable Mode When the OE# input impedance state. Device Bank 1 Model Number Megabit 01 Mbit Device Model Number Megabits 21 Mbit 31 Mbit 41 Mbit 16 ...

Page 17

Table 8.3 S29JL032H Sector Addresses - Top Boot Devices (Sheet Sector SA0 SA1 SA2 SA3 SA4 SA5 SA6 SA7 SA8 SA9 SA10 SA11 SA12 SA13 SA14 SA15 SA16 SA17 SA18 SA19 SA20 SA21 SA22 SA23 SA24 SA25 ...

Page 18

Table 8.3 S29JL032H Sector Addresses - Top Boot Devices (Sheet Sector SA32 SA33 SA34 SA35 SA36 SA37 SA38 SA39 SA40 SA41 SA42 SA43 SA44 SA45 SA46 SA47 SA48 SA49 SA50 SA51 SA52 SA53 SA54 SA55 SA56 SA57 ...

Page 19

Table 8.4 S29JL032H Sector Addresses - Bottom Boot Devices (Sheet Sector SA0 SA1 SA2 SA3 SA4 SA5 SA6 SA7 SA8 SA9 SA10 SA11 SA12 SA13 SA14 SA15 SA16 SA17 SA18 SA19 SA20 SA21 SA22 SA23 SA24 SA25 ...

Page 20

Table 8.4 S29JL032H Sector Addresses - Bottom Boot Devices (Sheet Sector SA39 SA40 SA41 SA42 SA43 SA44 SA45 SA46 SA47 SA48 SA49 SA50 SA51 SA52 SA53 SA54 SA55 SA56 SA57 SA58 SA59 SA60 SA61 SA62 SA63 SA64 ...

Page 21

Autoselect Mode The autoselect mode provides manufacturer and device identification, and sector protection verification, through identifier codes output on DQ7–DQ0. This mode is primarily intended for programming equipment to automatically match a device to be programmed with its corresponding ...

Page 22

Sector/Sector Block Protection and Unprotection Note: For the following discussion, the term “sector” applies to both sectors and sector blocks. A sector block consists of two or more adjacent sectors that are protected or unprotected at the same time ...

Page 23

Sector SA70 SA69-SA67 SA66-SA63 SA62-SA59 SA58-SA55 SA54-SA51 SA50-SA47 SA46-SA43 SA42-SA39 SA38-SA35 SA34-SA31 SA30-SA27 SA26-SA23 SA22-SA19 SA18-SA15 SA14-SA11 SA10-SA8 SA7 SA6 SA5 SA4 SA3 SA2 SA1 SA0 Sector protect/Sector Unprotect requires V system or via programming equipment. on page 55 shows ...

Page 24

Write Protect (WP#) The Write Protect function provides a hardware method of protecting certain boot sectors without using V This function is one of two provided by the WP#/ACC pin. If the system asserts V outermost 8 Kbyte boot ...

Page 25

START PLSCNT = 1 RESET Wait First Write Temporary Sector Cycle = 60h? Unprotect Mode Yes Set up sector address Sector Protect: Write 60h to sector address with A6=0, A3=0, A2=0, A1=1, A0=0 Wait ...

Page 26

... Customer Lockable: Secured Silicon Sector NOT Programmed or Protected At the Factory If the security feature is not required, the Secured Silicon Sector can be treated as an additional Flash memory space. The Secured Silicon Sector can be read any number of times, but can be programmed and locked only once. Note that the accelerated programming (ACC) and unlock bypass functions are not available when programming the Secured Silicon Sector ...

Page 27

Hardware Data Protection The command sequence requirement of unlock cycles for programming or erasing provides data protection against inadvertent writes (refer to hardware data protection measures prevent accidental erasure or programming, which might otherwise be caused by spurious system ...

Page 28

... Software support can then be device-independent, JEDEC ID-independent, and forward- and backward-compatible for the specified flash device families. Flash vendors can standardize their existing interfaces for long-term compatibility. This device enters the CFI Query mode when the system writes the CFI Query command, 98h, to address 55h in word mode (or address AAh in byte mode), any time the device is ready to read array data ...

Page 29

... August 31, 2009 S29JL032H_00_B8 Table 9.3 Device Geometry Definition Data N 4Eh 0016h Device Size = 2 50h 0002h Flash Device Interface description (refer to CFI publication 100) 52h 0000h 54h 0000h Max. number of byte in multi-byte write = 2 56h 0000h (00h = not supported) 58h 0002h Number of Erase Block Regions within device ...

Page 30

Addresses Addresses (Word Mode) (Byte Mode) 40h 41h 42h 43h 44h 45h 46h 47h 48h 49h 4Ah 4Bh 4Ch 4Dh 4Eh 4Fh 50h 57h 58h 59h 5Ah 5Bh Table 9.4 ...

Page 31

Command Definitions Writing specific address and data commands or sequences into the command register initiates device operations. Table 10.1 on page 37 and data values or writing them in the improper sequence may place the device in an unknown ...

Page 32

... Embedded Program or embedded Erase algorithm. on page 37 shows the address and data requirements for both command sequences. See also Sector Flash Memory Region on page 26 bypass modes are not available when the Secured Silicon Sector is enabled. 10.5 Byte/Word Program Command Sequence The system may program the device by word or byte, depending on the state of the BYTE# pin ...

Page 33

Unlock Bypass Command Sequence The unlock bypass feature allows the system to program bytes or words to a bank faster than using the standard program command sequence. The unlock bypass command sequence is initiated by first writing two unlock ...

Page 34

Chip Erase Command Sequence Chip erase is a six bus cycle operation. The chip erase command sequence is initiated by writing two unlock cycles, followed by a set-up command. Two additional unlock write cycles are then followed by the ...

Page 35

Notes 1. See Table 10.1 on page 37 2. See the section on DQ3 for information on the sector erase timer. August 31, 2009 S29JL032H_00_B8 Figure 10.2 Erase Operation START Write ...

Page 36

Erase Suspend/Erase Resume Commands The Erase Suspend command, B0h, allows the system to interrupt a sector erase operation and then read data from, or program data to, any sector not selected for erasure. The bank address is required when ...

Page 37

Command Sequence (Note 1) Addr Read (Note Reset (Note 7) 1 XXX Word 555 Manufacturer ID 4 Byte AAA Word 555 Device ID (Note 9) 6 Byte AAA Word 555 Secured Silicon Sector 4 Factory Protect (Note ...

Page 38

The data is 42h for customer locked, and 82h for not customer locked. Some current and most future Spansion devices (including future revisions of this device) will offer an option for programming and permanently locking the Secured Silicon Sector ...

Page 39

Notes Valid address for programming. During a sector erase operation, a valid address is any sector address within the sector being erased. During chip erase, a valid address is any non-protected sector address. 2. DQ7 should be ...

Page 40

After an erase command sequence is written, if all sectors selected for erasing are protected, DQ6 toggles for approximately 100 µs, then returns to reading array data. If not all selected sectors are protected, the Embedded Erase algorithm erases the ...

Page 41

DQ2: Toggle Bit II The “Toggle Bit II” on DQ2, when used with DQ6, indicates whether a particular sector is actively erasing (that is, the Embedded Erase algorithm is in progress), or whether that sector is erase-suspended. Toggle Bit ...

Page 42

DQ3: Sector Erase Timer After writing a sector erase command sequence, the system may read DQ3 to determine whether or not erasure has begun. (The sector erase timer does not apply to the chip erase command.) If additional sectors ...

Page 43

Absolute Maximum Ratings Storage Temperature, Plastic Packages Ambient Temperature with Power Applied Voltage with Respect to Ground, V A9, OE#, and RESET# WP#/ACC All other pins (Note 1) Output Short Circuit Current Notes 1. Minimum DC voltage on input ...

Page 44

Operating Ranges Industrial (I) Devices Ambient Temperature (T V Supply Voltages CC V for standard voltage range 2 3 Operating ranges define those limits between which the functionality of the device is guaranteed. 14. DC ...

Page 45

... Zero-Power Flash Figure 14.1 I CC1 500 Note Addresses are switching at 1 MHz Note °C August 31, 2009 S29JL032H_00_B8 Current vs. Time (Showing Active and Automatic Sleep Currents) 1000 1500 2000 2500 Time in ns Figure 14.2 Typical I vs. Frequency CC1 2 3 Frequency in MHz ...

Page 46

Test Conditions Note Diodes are IN3064 or equivalent. Output Load Output Load Capacitance, C (including jig capacitance) Input Rise and Fall Times Input Pulse Levels Input timing measurement reference levels Output timing measurement reference levels 16. Key To Switching ...

Page 47

AC Characteristics 17.1 Read-Only Operations Parameter JEDEC Std Read Cycle Time AVAV Address to Output Delay AVQV ACC t t Chip Enable to Output Delay ELQV Output Enable to Output Delay ...

Page 48

Hardware Reset (RESET#) Parameter JEDEC Std t Ready t Ready RPD t RB Note Not 100% tested. RY/BY# CE#, OE# RESET# RY/BY# CE#, OE# RESET ...

Page 49

Word/Byte Configuration (BYTE#) Parameter JEDEC Std ELFL/ ELFH t FLQZ t FHQV BYTE# DQ14–DQ0 Switching from word to byte mode BYTE# Switching from byte to DQ14–DQ0 word mode CE# WE# BYTE# Note Refer to the Erase/Program Operations ...

Page 50

Erase and Program Operations Parameter JEDEC Std t t AVAV AVWL AS t ASO t t WLAX AH t AHT t t DVWH WHDX DH t OEPH t t GHWL GHWL t t ...

Page 51

Addresses CE# OE# WE# Data RY/BY VCS Notes program address program data Illustration shows device in word mode WP#/ACC August 31, 2009 S29JL032H_00_B8 D ...

Page 52

Addresses CE# OE# WE# Data RY/BY# t VCS V CC Notes sector address (for Sector Erase Valid Address for reading status data (see 2. These waveforms are for the word mode. Figure 17.8 Back-to-back Read/Write ...

Page 53

Figure 17.9 Data# Polling Timings (During Embedded Algorithms) Addresses VA t ACC OEH WE# DQ7 DQ0–DQ6 t BUSY RY/BY# Note VA = Valid address. Illustration shows first status cycle after command ...

Page 54

Enter Erase Embedded Suspend Erasing Erase Erase Suspend WE# DQ6 DQ2 Note DQ2 toggles only when read at an address within an erase-suspended sector. The system may use OE# or CE# to toggle DQ2 and DQ6. 17.5 Temporary Sector Unprotect ...

Page 55

Figure 17.13 Sector/Sector Block Protect and Unprotect Timing Diagram RESET# SA, A6, A1, A0 Sector Group Protect/Unprotect Data 60h 1 µs CE# WE# OE# Note *For sector protect ...

Page 56

Figure 17.14 Alternate CE# Controlled Write (Erase/Program) Operation Timings Addresses WE# OE# CE# Data RESET# RY/BY# Notes 1. Figure indicates last two bus cycles of a program or erase operation program address sector address, PD ...

Page 57

Erase and Programming Performance Parameter Sector Erase Time Chip Erase Time Byte Program Time Word Program Time Accelerated Byte/Word Program Time Chip Program Time (Note 3) Notes 1. Typical program and erase times assume the following conditions: 25°C, V ...

Page 58

Physical Dimensions 20.1 TS 048—48-Pin Standard TSOP STANDARD PIN OUT (TOP VIEW SEE DETAIL 0. (N/2 TIPS) PARALLEL TO SEATING PLANE Package TS/TSR 048 Jedec MO-142 (D) DD Symbol MIN NOM ...

Page 59

... General Description Eliminated text in the S29JL032H Features section. Device Bus Operations Added Note and made changes to the S29JL032H Autoselect Codes table. Eliminated text from the Secured Silicon Sector Flash Memory Region section. Command Definitions Modified a note in the S29JL032H Command Definitions table. DC Characteristics Modified VOL Parameters ...

Page 60

... Word/Byte Configuration (BYTE#) Changed t condition from Min. to Max. FHQV 21.12 Revision B8 (August 31, 2009) Secured Silicon Sector Flash Memory Region Modified Section Section Added Factory Locked: Secured Silicon Sector Programmed and Protected At the Factory Customer Lockable: Secured Silicon Sector NOT Programmed or Protected ...

Page 61

... Spansion assumes no liability for any damages of any kind arising out of the use of the information in this document. Copyright © 2004-2009 Spansion Inc. All rights reserved. Spansion EcoRAM™ and combinations thereof, are trademarks and registered trademarks of Spansion LLC in the United States and other countries. ...