M41T256YMT7 STMicroelectronics, M41T256YMT7 Datasheet - Page 16

M41T256YMT7

Manufacturer Part Number

M41T256YMT7

Description

Real Time Clock Serial 256K (32Kx8)

Manufacturer

STMicroelectronics

Datasheet

1.M41T256YMT7.pdf

(30 pages)

Specifications of M41T256YMT7

Function

Clock, Calendar

Rtc Memory Size

32768 B

Supply Voltage (max)

5.5 V

Supply Voltage (min)

4.5 V

Maximum Operating Temperature

+ 70 C

Minimum Operating Temperature

- 25 C

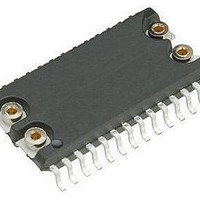

Mounting Style

SMD/SMT

Rtc Bus Interface

Serial

Package / Case

SO-44

Time Format

HH:MM:SS:hh

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

M41T256YMT7F

Manufacturer:

STMicroelectronics

Quantity:

135

2.5

Note:

Note:

Note:

16/30

Sleep mode

In order to minimize the battery current draw while in storage, the M41T256Y provides the

user with a battery “sleep mode,” which disconnects the RAM memory array from the

external Lithium battery normally used to provide non-volatile operation in the absence of

V

not needed.

The sleep mode will remove power from the RAM array only and not affect the data retention

of the TIMEKEEPER Registers (7FF0h through 7FFFh - this includes the Calibration

Register).

The sleep mode (SLP) Bit located in register 7FF8h (D6), must be set to a '1' by the user

while the device is powered by V

disconnect the RAM array from power until the next power-down cycle. This protects the

user from immediate data loss in the event he inadvertently sets the SLP Bit. Once V

below V

from the battery, resulting in both a lower battery current, and a loss of RAM data.

Upon initial battery attach or initial power application without the battery, the state of the SLP

Bit will be undetermined. Therefore, the SLP Bit should be initialized to '0' by the user.

Additional current reduction can be achieved by setting the STOP (ST) Bit in register 7FF9h

(D7), turning off the clock oscillator. This combination will result in the longest possible

battery life, but also loss of time and data. When the device is again powered-up, the user

should first read the SLP Bit to determine if the device is currently in sleep mode, then reset

the bit to '0' in order to disable the sleep mode (this will NOT be automatically taken care of

during the power-up).

See AN1570, “M41T256Y Sleep Mode Function” for more information on sleep mode and

battery lifetimes.

CC

. This can significantly extend the lifetime of the battery, when non-volatile operation is

SO

(V

BAT

), the sleep mode circuit will be engaged and the RAM array will be isolated

CC

. This will “arm” the sleep mode latch, but not actually

CC

falls