HFBR-0559 Avago Technologies US Inc., HFBR-0559 Datasheet - Page 2

HFBR-0559

Manufacturer Part Number

HFBR-0559

Description

Fiber Optics, Evaluation Kit

Manufacturer

Avago Technologies US Inc.

Datasheet

1.HFBR-0559.pdf

(16 pages)

Specifications of HFBR-0559

Silicon Manufacturer

Avago

Silicon Core Number

HFBR-5903/5903E/5903A

Kit Application Type

Communication & Networking

Application Sub Type

Ethernet Transceiver

Main Purpose

Interface, Ethernet

Embedded

No

Utilized Ic / Part

HFBR-5903, FDDL, Fast Ethernet Transceivers

Primary Attributes

FDDE & Fast Ethernet SFF Transceiver Compatible

Secondary Attributes

SONET OC-3/SDH STM-1

Description/function

Fiber Optic Kit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With/related Products

HFCT-5903E

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Contains lead / RoHS non-compliant

The HFBR-5903 is also useful for both ATM 100 Mb/s

interfaces and Fast Ethernet 100 Base-FX interfaces. The

ATM Forum User-Network Interface (UNI) Standard,

Version 3.0, defines the Physical Layer for 100 Mb/s

Multimode Fiber Interface for ATM in Section 2.3 to be

the FDDI PMD Standard. Likewise, the Fast Ethernet

Alliance defines the Physical Layer for 100 Base-FX for

Fast Ethernet to be the FDDI PMD Standard.

ATM applications for physical layers other than 100 Mb/

s Multimode Fiber Interface are supported by Avago

Technologies. Products are available for both the single-

mode and the multimode fiber SONET OC-3c (STS-3c),

SDH (STM-1) ATM interfaces and the 155 Mb/s-194 logic

output and the Signal Detect function. The Data output

is differential. The Signal Detect output is single-ended.

Both Data and Signal Detect outputs are PECL compat-

ible, ECL referenced (shifted) to a +3.3 V power supply.

The receiver outputs, Data Out and Data Out Bar, are

squelched at Signal Detect Deassert. That is, when the

light input power decreases to a typical -38 dBm or

less, the Signal Detect Deasserts, i.e. the Signal Detect

output goes to a PECL low state. This forces the receiver

outputs, Data Out and Data Out Bar to go to steady

PECL levels High and Low respectively.

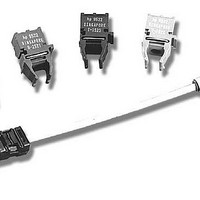

Package

The overall package concept for the Avago

Technologies transceiver consists of the following basic

elements; two optical subassemblies, an electrical

subassembly and the housing as illustrated in Figure 1.

Figure 1. Block Diagram.

DATA IN

DATA IN

2

DATA OUT

DATA OUT

SIGNAL

DETECT

QUANTIZER IC

LED DRIVER IC

R

T

X

X

SUPPLY

SUPPLY

R

T

X

X

GROUND

GROUND

The package outline drawing and pin out are shown in

Figures 2 and 3. The details of this package outline and

pin out are compliant with the multisource definition

of the 2 x 5 DIP. The low profile of the Avago

Technologies transceiver design complies with the

maximum height allowed for the MT-RJ connector over

the entire length of the package.

The optical subassemblies utilize a high-volume

assembly process together with low-cost lens elements

which result in a cost-effective building block.

The electrical subassembly consists of a high volume

multilayer printed circuit board on which the IC and

various surface-mounted passive circuit elements are

attached.

The receiver section includes an internal shield for the

electrical and optical subassemblies to ensure high

immunity to external EMI fields.

The outer housing is electrically conductive. The MT-RJ

port is molded of filled nonconductive plastic to

provide mechanical strength and electrical isolation.

The solder posts of the Avago Technologies design are

isolated from the internal circuit of the transceiver.

The transceiver is attached to a printed circuit board

with the ten signal pins and the two solder posts which

exit the bottom of the housing. The two solder posts

provide the primary mechanical strength to withstand

the loads imposed on the transceiver by mating with

the MT-RJ connectored fiber cables.

PIN PHOTODIODE

PRE-AMPLIFIER

SUBASSEMBLY

LED OPTICAL

SUBASSEMBLY

MT-RJ

RECEPTACLE