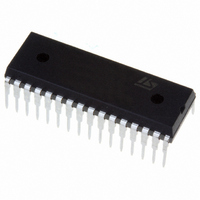

ST72F63BK4B1 STMicroelectronics, ST72F63BK4B1 Datasheet - Page 68

ST72F63BK4B1

Manufacturer Part Number

ST72F63BK4B1

Description

IC MCU 8BIT 16K FLASH 32-SDIP

Manufacturer

STMicroelectronics

Series

ST7r

Datasheet

1.ST72F63BD6U1TR.pdf

(186 pages)

Specifications of ST72F63BK4B1

Core Processor

ST7

Core Size

8-Bit

Speed

8MHz

Connectivity

I²C, SCI, USB

Peripherals

DMA, LVD, POR, PWM, WDT

Number Of I /o

19

Program Memory Size

16KB (16K x 8)

Program Memory Type

FLASH

Ram Size

512 x 8

Voltage - Supply (vcc/vdd)

4 V ~ 5.5 V

Data Converters

A/D 12x8b

Oscillator Type

External

Operating Temperature

0°C ~ 70°C

Package / Case

32-SDIP (0.400", 10.16mm)

Processor Series

ST72F6x

Core

ST7

Data Bus Width

8 bit

Data Ram Size

512 B

Interface Type

I2C, SCI

Maximum Clock Frequency

8 MHz

Number Of Programmable I/os

19

Number Of Timers

1

Maximum Operating Temperature

+ 70 C

Mounting Style

Through Hole

Development Tools By Supplier

ST7MDTU3-EPB/US, ST72F63B-SK/RAIS, ST7MDTU3-EMU3, STX-RLINK

Minimum Operating Temperature

0 C

On-chip Adc

8 bit, 8 Channel / 8 bit, 12 Channel

For Use With

497-5521 - EVAL BOARD LOW SPEED USB

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

- Current page: 68 of 186

- Download datasheet (3Mb)

On-chip peripherals

68/186

One Pulse mode

One Pulse mode enables the generation of a pulse when an external event occurs. This

mode is selected via the OPM bit in the CR2 register.

The One Pulse mode uses the input Capture1 function and the output Compare1 function.

Procedure

To use One Pulse mode:

1.

2.

3.

Figure 37. One Pulse mode cycle

Then, on a valid event on the ICAP1 pin, the counter is initialized to FFFCh and OLVL2 bit is

loaded on the OCMP1 pin, the ICF1 bit is set and the value FFFDh is loaded in the IC1R

register.

Because the ICF1 bit is set when an active edge occurs, an interrupt can be generated if the

ICIE bit is set.

Clearing the input Capture interrupt request (that is, clearing the ICFi bit) is done in two

steps:

1.

2.

Load the OC1R register with the value corresponding to the length of the pulse (see the

formula in the opposite column).

Select the following in the CR1 register:

–

–

–

Select the following in the CR2 register:

–

–

–

Reading the SR register while the ICFi bit is set.

An access (read or write) to the ICiLR register.

Using the OLVL1 bit, select the level to be applied to the OCMP1 pin after the

pulse.

Using the OLVL2 bit, select the level to be applied to the OCMP1 pin during the

pulse.

Select the edge of the active transition on the ICAP1 pin with the IEDG1 bit (the

ICAP1 pin must be configured as floating input).

Set the OC1E bit, the OCMP1 pin is then dedicated to the output Compare 1

function.

Set the OPM bit.

Select the timer clock CC[1:0] (see

event occurs

on ICAP1

Doc ID 7516 Rev 8

When

Counter

= OC1R

When

OCMP1 = OLVL2

Table

OCMP1 = OLVL1

ICR1 = Counter

Counter is reset

ICF1 bit is set

to FFFCh

24).

ST7263Bxx

Related parts for ST72F63BK4B1

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER LOW COST ST7

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

LOW SPEED USB 8-BIT MCU FAMILY WITH FLASH/ROM, UP TO 512 BYTES RAM, 8-BIT ADC, WDG, TIMER, SCI & I�C

Manufacturer:

STMICROELECTRONICS [STMicroelectronics]

Datasheet:

Part Number:

Description:

STMicroelectronics [RIPPLE-CARRY BINARY COUNTER/DIVIDERS]

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

STMicroelectronics [LIQUID-CRYSTAL DISPLAY DRIVERS]

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

BOARD EVAL FOR MEMS SENSORS

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

NPN TRANSISTOR POWER MODULE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

TURBOSWITCH ULTRA-FAST HIGH VOLTAGE DIODE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

DIODE / SCR MODULE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

DIODE / SCR MODULE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

Search -----> STE16N100

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

Search ---> STE53NA50

Manufacturer:

STMicroelectronics

Datasheet: