AT90USB162-16AUR Atmel, AT90USB162-16AUR Datasheet - Page 160

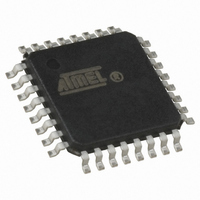

AT90USB162-16AUR

Manufacturer Part Number

AT90USB162-16AUR

Description

IC AVR MCU 16K FLASH 32TQFP

Manufacturer

Atmel

Series

AVR® 90USBr

Datasheet

1.AT90USB82-16MU.pdf

(307 pages)

Specifications of AT90USB162-16AUR

Core Processor

AVR

Core Size

8-Bit

Speed

16MHz

Connectivity

EBI/EMI, PS/2, SPI, UART/USART, USB

Peripherals

Brown-out Detect/Reset, POR, PWM, WDT

Number Of I /o

22

Program Memory Size

16KB (16K x 8)

Program Memory Type

FLASH

Eeprom Size

512 x 8

Ram Size

512 x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

32-TQFP, 32-VQFP

Processor Series

AT90USBx

Core

AVR8

Data Bus Width

8 bit

Data Ram Size

512 B

Interface Type

SPI/USART/debugWIRE

Maximum Clock Frequency

16 MHz

Number Of Programmable I/os

22

Number Of Timers

2

Operating Supply Voltage

2.7 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

EWAVR, EWAVR-BL

Development Tools By Supplier

ATAVRDRAGON, ATSTK500, ATSTK600, ATSTK525, ATSTK526, ATAVRISP2, ATAVRONEKIT, AT90USBKEY, ATEVK525

Minimum Operating Temperature

- 40 C

Cpu Family

AT90

Device Core

AVR

Device Core Size

8b

Frequency (max)

16MHz

Total Internal Ram Size

512Byte

# I/os (max)

22

Number Of Timers - General Purpose

2

Operating Supply Voltage (typ)

3.3/5V

Operating Supply Voltage (max)

5.5V

Operating Supply Voltage (min)

2.7V

Instruction Set Architecture

RISC

Operating Temp Range

-40C to 85C

Operating Temperature Classification

Industrial

Mounting

Surface Mount

Pin Count

32

Package Type

TQFP

For Use With

ATSTK600-TQFP32 - STK600 SOCKET/ADAPTER 32-TQFPATSTK526 - KIT STARTER FOR AT90USB82/162ATAVRDRAGON - KIT DRAGON 32KB FLASH MEM AVRATSTK525 - KIT STARTER FOR AT90USBAT90USBKEY2 - KIT DEMO FOR AT90USB

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Data Converters

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

AT90USB162-16AU

AT90USB162-16AURTR

AT90USB162-16AUTR

AT90USB162-16AUTR

AT90USB162-16AURTR

AT90USB162-16AUTR

AT90USB162-16AUTR

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

AT90USB162-16AUR

Manufacturer:

Atmel

Quantity:

2 751

- Current page: 160 of 307

- Download datasheet (4Mb)

17.7.2

160

AT90USB82/162

Asynchronous Data Recovery

Figure 17-5. Start Bit Sampling

When the clock recovery logic detects a high (idle) to low (start) transition on the RxDn line, the

start bit detection sequence is initiated. Let sample 1 denote the first zero-sample as shown in

the figure. The clock recovery logic then uses samples 8, 9, and 10 for Normal mode, and sam-

ples 4, 5, and 6 for Double Speed mode (indicated with sample numbers inside boxes on the

figure), to decide if a valid start bit is received. If two or more of these three samples have logical

high levels (the majority wins), the start bit is rejected as a noise spike and the Receiver starts

looking for the next high to low-transition. If however, a valid start bit is detected, the clock recov-

ery logic is synchronized and the data recovery can begin. The synchronization process is

repeated for each start bit.

When the receiver clock is synchronized to the start bit, the data recovery can begin. The data

recovery unit uses a state machine that has 16 states for each bit in Normal mode and eight

states for each bit in Double Speed mode.

the parity bit. Each of the samples is given a number that is equal to the state of the recovery

unit.

Figure 17-6. Sampling of Data and Parity Bit

The decision of the logic level of the received bit is taken by doing a majority voting of the logic

value to the three samples in the center of the received bit. The center samples are emphasized

on the figure by having the sample number inside boxes. The majority voting process is done as

follows: If two or all three samples have high levels, the received bit is registered to be a logic 1.

If two or all three samples have low levels, the received bit is registered to be a logic 0. This

majority voting process acts as a low pass filter for the incoming signal on the RxDn pin. The

recovery process is then repeated until a complete frame is received. Including the first stop bit.

Note that the Receiver only uses the first stop bit of a frame.

Figure 17-7

of the next frame.

(U2X = 0)

(U2X = 1)

Sample

Sample

(U2X = 0)

(U2X = 1)

Sample

Sample

RxD

RxD

shows the sampling of the stop bit and the earliest possible beginning of the start bit

0

0

IDLE

0

1

1

1

1

2

2

3

2

3

2

4

4

5

3

5

3

6

6

Figure 17-6

7

4

7

4

8

8

START

BIT n

9

5

9

5

10

10

shows the sampling of the data bits and

11

11

6

6

12

12

13

13

7

7

14

14

15

8

15

8

16

16

1

1

1

1

7707F–AVR–11/10

2

BIT 0

3

2

Related parts for AT90USB162-16AUR

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Atmel Corporation

Datasheet:

Part Number:

Description:

MCU AVR USB 16K FLASH 32-TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR USB 16K FLASH 32-QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC AVR MCU 16K FLASH 32QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools PROTOTYPE BRD FOR AT90USB162

Manufacturer:

Olimex Ltd.

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools DEV BRD FOR AT90USB162

Manufacturer:

Olimex Ltd.

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools Demo board f/AVR MCU & AT90USB

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Monolithic Integrated Feature Phone Circuit

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Multistandard Video-IF and Quasi Parallel Sound Processing

Manufacturer:

ATMEL Corporation

Datasheet: