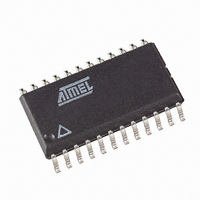

AT90PWM216-16SUR Atmel, AT90PWM216-16SUR Datasheet - Page 214

AT90PWM216-16SUR

Manufacturer Part Number

AT90PWM216-16SUR

Description

MCU AVR 16K FLASH 16MHZ 24SOIC

Manufacturer

Atmel

Series

AVR® 90PWM Lightingr

Datasheet

1.AT90PWM216-16SU.pdf

(359 pages)

Specifications of AT90PWM216-16SUR

Core Processor

AVR

Core Size

8-Bit

Speed

16MHz

Connectivity

SPI, UART/USART

Peripherals

Brown-out Detect/Reset, POR, PWM, WDT

Number Of I /o

19

Program Memory Size

16KB (16K x 8)

Program Memory Type

FLASH

Eeprom Size

512 x 8

Ram Size

1K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 8x10b; D/A 1x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 105°C

Package / Case

24-SOIC (7.5mm Width)

Processor Series

AT90PWMx

Core

AVR8

3rd Party Development Tools

EWAVR, EWAVR-BL

Development Tools By Supplier

ATAVRDRAGON, ATSTK500, ATSTK600, ATAVRISP2, ATAVRONEKIT, ATAVRFBKIT, ATAVRISP2

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- Current page: 214 of 359

- Download datasheet (6Mb)

19.3.2

19.3.3

214

AT90PWM216/316

Parity Bit Calculation

Manchester encoding

The frame format used by the EUSART can be configured through the following

USART/EUSART registers:

USBS (UCSRC register of USART) and EUSBS (EUCSRB register of EUSART) select the num-

ber of stop bits to be processed respectively by the transmiter and the receiver. The receiver

stores the two stop bit values when configured in Manchester mode. When configured in level

encoded mode, the second stop bit is ignored (behavior similar as the USART).

The parity bit behavior is similar to the USART mode, except for the Manchester encoded mode,

where no parity bit can be inserted or detected (should be configured to none with the UPM1:0

bits. The parity bit is calculated by doing an exclusive-or of all the data bits. If odd parity is used,

the result of the exclusive or is inverted. The relation between the parity bit and data bits is as

follows:

If used, the parity bit is located between the last data bit and first stop bit of a serial frame.

Manchester encoding (also know as Biphase Code) is a synchronous clock encoding technique

used to encode the clock and data of a synchronous bit stream. In this technique, the actual

binary data to be transmitted are not sent as a sequence of logic 1's and 0's as in level encoded

way as in standard USART (known technically as Non Return to Zero (NRZ)). Instead, the bits

are translated into a slightly different format that has a number of advantages over using straight

binary encoding (i.e. NRZ).

Manchester encoding follows the rules:

• UTxS3:0 and URxS3:0 (EUCSRA of EUSART register) select the number of data bits per

• UPM1:0 bits enable and set the type of parity bit (when configured in Manchester mode, the

• If the original data is a Logic 1, the Manchester code is: 0 to 1 (upward transition at bit center)

• If the original data is a Logic 0, the Manchester code is: 1 to 0 (downward transition at bit

frame

parity should be fixed to none).

center)

– Stop bits insertion for transmition

– Stop bits value read access in reception

P

P

d

odd

n

even

Parity bit using even parity

Parity bit using odd parity

Data bit n of the character

P

P

even

odd

=

=

d

d

n 1

n 1

–

–

⊕

⊕

…

…

⊕

⊕

d

d

3

3

⊕

⊕

d

d

2

2

⊕

⊕

d

d

1

1

⊕

⊕

d

d

0

0

⊕

⊕

0

1

7710E–AVR–08/10

Related parts for AT90PWM216-16SUR

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Atmel Corporation

Datasheet:

Part Number:

Description:

8-bit Microcontroller with 16K Bytes In-System Programmable flash

Manufacturer:

ATMEL [ATMEL Corporation]

Datasheet:

Part Number:

Description:

MCU AVR 16K ISP FLSH 16MHZ24SOIC

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Monolithic Integrated Feature Phone Circuit

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Multistandard Video-IF and Quasi Parallel Sound Processing

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

High-performance EE PLD

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

8-bit Flash Microcontroller

Manufacturer:

ATMEL Corporation

Datasheet: