MC908AZ60ACFUE Freescale Semiconductor, MC908AZ60ACFUE Datasheet - Page 358

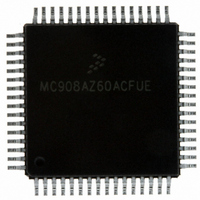

MC908AZ60ACFUE

Manufacturer Part Number

MC908AZ60ACFUE

Description

IC MCU FLASH 8.4MHZ 60K 64QFP

Manufacturer

Freescale Semiconductor

Series

HC08r

Datasheet

1.MC908AZ60ACFUER.pdf

(414 pages)

Specifications of MC908AZ60ACFUE

Core Processor

HC08

Core Size

8-Bit

Speed

8.4MHz

Connectivity

CAN, SCI, SPI

Peripherals

LVD, POR, PWM

Number Of I /o

52

Program Memory Size

60KB (60K x 8)

Program Memory Type

FLASH

Eeprom Size

1K x 8

Ram Size

2K x 8

Voltage - Supply (vcc/vdd)

4.5 V ~ 5.5 V

Data Converters

A/D 15x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

64-QFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC908AZ60ACFUE

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Part Number:

MC908AZ60ACFUE

Manufacturer:

FREESCALE

Quantity:

20 000

Company:

Part Number:

MC908AZ60ACFUE1L87J

Manufacturer:

TEMIC

Quantity:

350

Company:

Part Number:

MC908AZ60ACFUER

Manufacturer:

FREESCALE

Quantity:

5 560

Company:

Part Number:

MC908AZ60ACFUER

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 358 of 414

- Download datasheet (5Mb)

Byte Data Link Controller (BDLC)

TSIFR, TMIFR1, and TMIFR0 — Transmit In-Frame Response Control Bits

358

These three bits control the type of in-frame response being sent. The programmer should not set

more than one of these control bits to a 1 at any given time. However, if more than one of these three

control bits are set to 1, the priority encoding logic will force these register bits to a known value as

shown in

they will be encoded as 010. However, when these bits are read back, they will read 011.

The BDLC supports the in-frame response (IFR) feature of J1850 by setting these bits correctly. The

four types of J1850 IFR are shown below. The purpose of the in-frame response modes is to allow

multiple nodes to acknowledge receipt of the data by responding with their personal ID or physical

address in a concatenated manner after they have seen the EOD symbol. If transmission arbitration is

lost by a node while sending its response, it continues to transmit its ID/address until observing its

unique byte in the response stream. For VPW modulation, because the first bit of the IFR is always

passive, a normalization bit (active) must be generated by the responder and sent prior to its

ID/address byte. When there are multiple responders on the J1850 bus, only one normalization bit is

sent which assists all other transmitting nodes to sync up their response.

NB = Normalization Bit

ID = Identifier (usually the physical address of the responder(s))

HEADER = Specifies one of three frame lengths

HEADER

HEADER

HEADER

HEADER

Table

TYPE 0 — NO IFR

TYPE 1 — SINGLE BYTE TRANSMITTED FROM A SINGLE RESPONDER

TYPE 2 — SINGLE BYTE TRANSMITTED FROM MULTIPLE RESPONDERS

TYPE 3 — MULTIPLE BYTES TRANSMITTED FROM A SINGLE RESPONDER

MC68HC908AZ60A • MC68HC908AS60A • MC68HC908AS60E Data Sheet, Rev. 6

Write/Read

27-4. For example, if 011 is written to TSIFR, TMIFR1, and TMIFR0, then internally

TSIFR

0

1

0

0

Figure 27-18. Types of In-Frame Response (IFR)

DATA FIELD

DATA FIELD

Table 27-4. BDLC Transmit In-Frame Response

DATA FIELD

DATA FIELD

Write/Read

TMIFR1

X

0

1

0

Control Bit Priority Encoding

CRC

CRC

CRC

CRC

Write/Read

TMIFR0

0

X

X

1

NB

NB

NB

ID1

ID

Actual

TSIFR

IFR DATA FIELD

0

1

0

0

TMIFR1

Actual

0

0

1

0

ID N

TMIFR0

Actual

Freescale Semiconductor

0

0

0

1

(OPTIONAL)

CRC

Related parts for MC908AZ60ACFUE

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: