CDB42448 Cirrus Logic Inc, CDB42448 Datasheet - Page 38

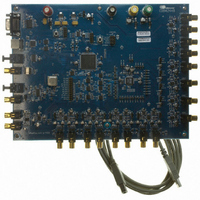

CDB42448

Manufacturer Part Number

CDB42448

Description

BOARD EVAL FOR CS42448 CODEC

Manufacturer

Cirrus Logic Inc

Specifications of CDB42448

Main Purpose

Audio, CODEC

Embedded

Yes, FPGA / CPLD

Utilized Ic / Part

CS42448

Primary Attributes

24-Bit, 192 kHz, 6 ADCs: 102dB Dynamic Range, 8 DACs: 105dB Dynamic Range

Secondary Attributes

Time Division Multiplexed (TDM), I2C, and SPI Interface, Popguard® Technology

Description/function

Audio CODECs

Operating Supply Voltage

5 V to 12 V

Product

Audio Modules

For Use With/related Products

CS42448

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Contains lead / RoHS non-compliant

Other names

598-1151

38

4.9

4.10

4.11

Recommended Power-Up Sequence

1. Hold RST low until the power supply and clocks are stable. In this state, the control port is reset to its

2. Bring RST high. The device will initially be in a low power state with VQ low. All features will default as

3. Perform a write operation to the Power Control register

4. Load the desired register settings while keeping the PDN bit set to ‘1’b.

5. Mute all DACs. Muting the DACs suppresses any noise associated with the CODEC's first initialization

6. Set the PDN bit in the power control register to ‘0’b. VQ will ramp to approximately VA/2 according to

7. Following approximately 2000 LRCK cycles, the device is initialized and ready for normal operation.

8. After the CODEC is initialized, wait ~90 LRCK cycles (~1.9 ms @48 kHz) and then un-mute the DACs.

9. Normal operation begins.

Reset and Power-Up

It is recommended that reset be activated if the analog or digital supplies drop below the recommended op-

erating condition to prevent power-glitch-related issues.

The delta-sigma modulators settle in a matter of microseconds after the analog section is powered, either

through the application of power or by setting the RST pin high. However, the voltage reference will take

much longer to reach a final value due to the presence of external capacitance on the ADC/DAC_FILT+

pins. A time delay of approximately 400 ms is required after applying power to the device or after exiting a

reset state. During this voltage reference ramp delay, all serial ports and DAC outputs will be automatically

muted.

Power Supply, Grounding, and PCB Layout

As with any high-resolution converter, the CS42448 requires careful attention to power supply and ground-

ing arrangements if its potential performance is to be realized.

rangements, with VA connected to clean supplies. VD, which powers the digital circuitry, may be run from

the system logic supply. Alternatively, VD may be powered from the analog supply via a ferrite bead. In this

case, no additional devices should be powered from VD.

Extensive use of power and ground planes, ground plane fill in unused areas and surface mount decoupling

capacitors are recommended. Decoupling capacitors should be placed as close to the pins of the CS42448

as possible. The low value ceramic capacitor should be closest to the pin and should be mounted on the

same side of the board as the CS42448 to minimize inductance effects. All signals, especially clocks, should

be kept away from the ADC/DAC_FILT+, VQ pins in order to avoid unwanted coupling into the modulators.

The ADC/DAC_FILT+ and VQ decoupling capacitors, particularly the 0.1 µF, must be positioned to mini-

mize the electrical path from ADC/DAC_FILT+ and AGND. The CDB42448 evaluation board demonstrates

the optimum layout and power supply arrangements.

For optimal heat dissipation from the package, it is recommended that the area directly under the part be

filled with copper and tied to the ground plane. The use of vias connecting the topside ground to the back-

side ground is also recommended.

default settings and VQ will remain low.

described in the

set bit 0 to a ‘1’b. This will place the device in a power down state.

after power is applied.

the Popguard specification in section

“Register Quick Reference” on page

“Popguard” on page

39.

(“Power Control (Address 02h)” on page

Figure 2

28.

shows the recommended power ar-

CS42448

DS648F3

42) to