LSN2-T/10-D12N-C Murata Power Solutions Inc, LSN2-T/10-D12N-C Datasheet - Page 11

LSN2-T/10-D12N-C

Manufacturer Part Number

LSN2-T/10-D12N-C

Description

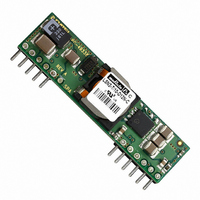

CONV DC/DC 50W 10A 0.75-5V SIP

Manufacturer

Murata Power Solutions Inc

Series

LSN2r

Type

Point of Load (POL) Non-Isolatedr

Datasheet

1.LSN2-T10-W3N-C.pdf

(15 pages)

Specifications of LSN2-T/10-D12N-C

Number Of Outputs

1

Output

0.75 ~ 5V

Power (watts)

50W

Mounting Type

Through Hole

Voltage - Input

8.3 ~ 14V

Package / Case

12-SIP Module

1st Output

0.75 ~ 5 VDC @ 10A

Size / Dimension

2.00" L x 0.32" W x 0.50" H (50.8mm x 8.1mm x 12.7mm)

Power (watts) - Rated

50W

Operating Temperature

-40°C ~ 85°C

Efficiency

95%

Approvals

CSA, EN, UL

Output Power

50 W

Input Voltage Range

8.3 V to 14 V

Input Voltage (nominal)

12 V

Output Voltage (channel 1)

0.75 V to 5 V

Output Current (channel 1)

10 A

Package / Case Size

SIP

Output Type

Low Voltage Selectable

Output Voltage

0.75 V to 5 V

Product

Non-Isolated / POL

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

3rd Output

-

2nd Output

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

811-1801

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

LSN2-T/10-D12N-C

Manufacturer:

MURATA/村田

Quantity:

20 000

other method. Several standard sequencing architectures are prevalent. They

are concerned with three factors:

difference relationship is important for systems very concerned about possible

latchup of programmable devices or overdriving ESD diodes. Lower slew

rates avoid overcurrent shutdown during bypass cap charge-up.

ferent respective fi nal set point voltages. During the ramp, their voltages are

nearly identical. This avoids problems with large currents fl owing between

logic systems which are not initialized yet. Since both end voltages are differ-

ent, each converter reaches it’s setpoint voltage at a different time.

fi nal voltages at about the same time.

■

■

■

For most systems, the time relationship is the dominant factor. The voltage

In Figure 8, two POL’s ramp up at the same rate until they reach their dif-

Figure 9 shows two POLs with different slew rates in order to reach differing

The time relationship between the Master and Slave voltages

The voltage difference relationship between the Master and Slave

The voltage slew rate (ramp slope) of each converter’s output.

Figure 8. Coincident or Simultaneous Phasing (Identical Slew Rates)

Figure 9. Proportional or Ratiometric Phasing (Identical V

OUT

Time)

www.murata-ps.com

for two converters. Figure 10 is called “Inclusive” because the later starting

POL fi nishes inside the earlier POL. The timing in Figure 10 is more easily built

using a combined digital sequence controller and the Sequence/Track pin.

relationship staggered approximately the same at power-up and power-down.

Operation

To use the Sequence pin after power start-up stabilizes, apply a rising external

voltage to the Sequence input. As the voltage rises, the output voltage will

track the Sequence input (gain = 1). The output voltage will stop rising when

it reaches the normal set point for the converter. The Sequence input may op-

tionally continue to rise without any effect on the output. Keep the Sequence

input voltage below the converter’s input supply voltage.

until the Sequence input falls below the set point.

below show simple RC networks but you may also use operational amplifi ers,

D/A converters, etc.

Figure 11. Staggered or Sequential Phasing—Exclusive (Fixed Cascaded Delays)

Figures 10 and 11 show both delayed start up and delayed fi nal voltages

Figure 11 is the same strategy as Figure 10 but with an “exclusive” timing

Use a similar strategy on power down. The output voltage will stay constant

Any strategy may be used to deliver the power up/down ramps. The circuits

Figure 10. Staggered or Sequential Phasing—Inclusive (Fixed Delays)

Selectable-Output DC/DC Converters

25 Jun 2010

Non-isolated, DOSA-SIP, 6/10/16A

LSN2 Series

MDC_LSN2.B07Δ

email: sales@murata-ps.com

Page 11 of 15