ATMEGA168-20PU Atmel, ATMEGA168-20PU Datasheet - Page 97

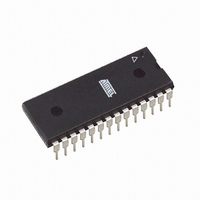

ATMEGA168-20PU

Manufacturer Part Number

ATMEGA168-20PU

Description

IC AVR MCU 16K 20MHZ 28DIP

Manufacturer

Atmel

Series

AVR® ATmegar

Datasheets

1.ATAVRTS2080B.pdf

(378 pages)

2.ATMEGA48-20AU.pdf

(35 pages)

3.ATMEGA88-20MU.pdf

(33 pages)

4.ATMEGA168-20AU.pdf

(359 pages)

Specifications of ATMEGA168-20PU

Core Processor

AVR

Core Size

8-Bit

Speed

20MHz

Connectivity

I²C, SPI, UART/USART

Peripherals

Brown-out Detect/Reset, POR, PWM, WDT

Number Of I /o

23

Program Memory Size

16KB (8K x 16)

Program Memory Type

FLASH

Eeprom Size

512 x 8

Ram Size

1K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 6x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

28-DIP (0.300", 7.62mm)

Processor Series

ATMEGA16x

Core

AVR8

Data Bus Width

8 bit

Data Ram Size

1 KB

Interface Type

2-Wire, SPI, USART, Serial

Maximum Clock Frequency

20 MHz

Number Of Programmable I/os

23

Number Of Timers

3

Operating Supply Voltage

2.7 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

Through Hole

3rd Party Development Tools

EWAVR, EWAVR-BL

Development Tools By Supplier

ATAVRDRAGON, ATSTK500, ATSTK600, ATAVRISP2, ATAVRONEKIT

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 6 Channel

A/d Inputs

6-Channel, 10-Bit

Cpu Speed

20 MIPS

Eeprom Memory

512 Bytes

Input Output

23

Interface

I2C/SPI/UART/USART

Memory Type

Flash

Number Of Bits

8

Package Type

28-pin PDIP

Programmable Memory

16K Bytes

Timers

2-8-bit, 1-16-bit

Voltage, Range

4.5-5.5 V

Controller Family/series

AVR MEGA

No. Of I/o's

23

Eeprom Memory Size

512Byte

Ram Memory Size

1KB

Rohs Compliant

Yes

For Use With

ATSTK600-TQFP32 - STK600 SOCKET/ADAPTER 32-TQFPATSTK600 - DEV KIT FOR AVR/AVR32770-1007 - ISP 4PORT ATMEL AVR MCU SPI/JTAGATAVRDRAGON - KIT DRAGON 32KB FLASH MEM AVRATAVRISP2 - PROGRAMMER AVR IN SYSTEMATJTAGICE2 - AVR ON-CHIP D-BUG SYSTEM

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

ATMEGA168-20PU

Manufacturer:

ATMEL/爱特梅尔

Quantity:

20 000

- ATAVRTS2080B PDF datasheet

- ATMEGA48-20AU PDF datasheet #2

- ATMEGA88-20MU PDF datasheet #3

- ATMEGA168-20AU PDF datasheet #4

- Current page: 97 of 359

- Download datasheet (3Mb)

12.7

2545E–AVR–02/05

Timer/Counter Timing Diagrams

one allows the OC0A pin to toggle on Compare Matches if the WGM02 bit is set. This option is

not available for the OC0B pin (see

visible on the port pin if the data direction for the port pin is set as output. The PWM waveform is

generated by clearing (or setting) the OC0x Register at the compare match between OCR0x and

TCNT0 when the counter increments, and setting (or clearing) the OC0x Register at compare

match between OCR0x and TCNT0 when the counter decrements. The PWM frequency for the

output when using phase correct PWM can be calculated by the following equation:

The N variable represents the prescale factor (1, 8, 64, 256, or 1024).

The extreme values for the OCR0A Register represent special cases when generating a PWM

waveform output in the phase correct PWM mode. If the OCR0A is set equal to BOTTOM, the

output will be continuously low and if set equal to MAX the output will be continuously high for

non-inverted PWM mode. For inverted PWM the output will have the opposite logic values.

At the very start of period 2 in

there is no Compare Match. The point of this transition is to guarantee symmetry around BOT-

TOM. There are two cases that give a transition without Compare Match.

• OCRnx changes its value from MAX, like in

• The timer starts counting from a value higher than the one in OCRnx, and for that reason

The Timer/Counter is a synchronous design and the timer clock (clk

clock enable signal in the following figures. The figures include information on when interrupt

flags are set.

shows the count sequence close to the MAX value in all modes other than phase correct PWM

mode.

Figure 12-8. Timer/Counter Timing Diagram, no Prescaling

Figure 12-9

OCn pin value is the same as the result of a down-counting Compare Match. To ensure

symmetry around BOTTOM the OCnx value at MAX must correspond to the result of an up-

counting Compare Match.

misses the Compare Match and hence the OCnx change that would have happened on the

way up.

TCNTn

(clk

TOVn

clk

clk

I/O

I/O

Tn

/1)

shows the same timing data, but with the prescaler enabled.

Figure 12-8

MAX - 1

contains timing data for basic Timer/Counter operation. The figure

Figure 12-7

Table 12-7 on page

f

OCnxPCPWM

OCnx has a transition from high to low even though

MAX

Figure

=

----------------- -

N 510

12-7. When the OCR0A value is MAX the

f

clk_I/O

⋅

101). The actual OC0x value will only be

ATmega48/88/168

BOTTOM

T0

) is therefore shown as a

BOTTOM + 1

97

Related parts for ATMEGA168-20PU

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Atmel Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Atmel Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

IC AVR MCU 16K 20MHZ 32TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC AVR MCU 16K 20MHZ 32-QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR 16K FLASH 15MHZ 32-TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR 16K FLASH 15MHZ 32-QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC AVR MCU 16K 20MHZ 32TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR 16KB FLASH 20MHZ 32QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR 16KB FLASH 20MHZ 32TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC MCU AVR 16K FLASH 32-QFN

Manufacturer:

Atmel

Datasheet: