MPC8360E-MDS-PBE Freescale Semiconductor, MPC8360E-MDS-PBE Datasheet - Page 3

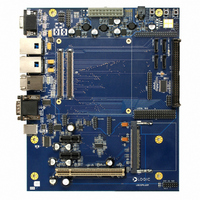

MPC8360E-MDS-PBE

Manufacturer Part Number

MPC8360E-MDS-PBE

Description

BOARD PROCESSOR FOR MPC8360E

Manufacturer

Freescale Semiconductor

Specifications of MPC8360E-MDS-PBE

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Technical Specifications

• e300 Power Architecture core operating

• QUICC Engine technology initially operating

from 266 MHz to 667 MHz

up to 500 MHz

32-bit, high-performance superscalar core

1,261 MIPS at 667 MHz; 503 MIPS

at 266 MHz

Double-precision floating point, integer,

load/store, system register and branch

processor units

32 KB data and 32 KB instruction cache

with line-locking support

Two 32-bit RISC controllers

for flexible support of the

communications peripherals

Serial DMA channel for receive and

transmit on all serial channels

QUICC Engine peripheral request

interface for Integrated Security, PCI,

IEEE Std 1588™

Eight UCCs supporting the following

protocols and interfaces:

·· 10/100/1000 Mbps Ethernet

·· IEEE Std 1588 protocol supported

·· ATM SAR supporting AAL5, AAL2,

·· Inverse multiplexing for ATM (IMA)

·· POS up to 622 Mbps

·· Transparent

·· HDLC

·· Multi-link, multi-class PPP

·· HDLC bus

·· UART

·· BISYNC

One multi-channel communications

controller (MCC), supporting:

·· 256 TDM channels

·· Transparent and HDLC mode

·· Support for Signaling System

·· Almost any combination of subgroups

Two UTOPIA/POS interfaces supporting

up to 128 multi-PHY each

Two serial peripheral interfaces (SPIs)

AAL1, AAL0, TM 4.0 CBR, VBR,

UBR traffic types, up to 64 KB

external connections

per channel

Number 7 (SS7)

can be multiplexed to single or multiple

TDM interfaces

• USB interface

• DDR memory controller

• PCI interface

• Integrated security (MPC8360E and

(USB 2.0 full/low speed compatible)

MPC8358E only)

Eight TDM interfaces, supporting:

·· Aggregate bandwidth of 64 kbps

·· Maximum of 16 Mbps and 256

·· 2,048 bytes of SI RAM (1,024 entries)

·· Eight programmable strobes

·· Bit or byte resolution

·· Independent transmit and receive

·· T1, CEPT, T1/E1, T3/E3, pulse-code

16 independent baud rate generators

Four independent 16-bit timers that can

be interconnected as two 32-bit timers

Two SPI ports that can be configured

as an Ethernet management port for

management data input/output (MDIO),

while the other can be configured for

cost-efffective serial peripherals; the

SPI also has a CPU mode that can

be configured by the CPU and not

through the QUICC Engine

Programmable timing supporting

DDR-1/2 SDRAM

2 x 32-bit (MPC8360E only) or

1 x 32/64-bit data interface; up to

333 MHz data rate

Four banks of memory, each up to 1 GB

Full ECC support

One 32-bit PCI 2.3 bus controller

(3.3V I/O; up to 66 MHz)

Public key execution

(RSA and Diffie-Hellman)

Data encryption standard execution

(DES and 3DES)

Advanced encryption standard

(AES) execution

ARC-4 execution

(RC4-compatible algorithm)

Message digest execution

(SHA, MD5, HMAC)

Random number generation (RNG)

and 256 channels

channels on a single TDM link

routing, frame synchronization

modulation highway, ISDN primary/basic

rate, Freescale interchip digital link (IDL)

and user-defined TDM serial interfaces

• Local bus controller

• Dual UART (DUART)

• Dual I

• Four-channel DMA controller

• General-purpose parallel I/O

• IEEE 1149.1 JTAG test access port

• Package option: 37.5 mm X 37.5 mm

• Process technology: 130 nm CMOS

• Voltage: 1.2V core voltage with 3.3V,

(master or slave mode)

740 TBGA (MPC8360E, MPC8358E);

29 mm x 29 mm 668 PBGA (MPC8358 only)

2.5V and 1.8V I/O

Multiplexed 32-bit address and

data operating up to 133 MHz

32-, 16- and 8-bit port

sizes controlled by on-chip

memory controller

2

C interfaces