AD8337-EVALZ Analog Devices Inc, AD8337-EVALZ Datasheet - Page 22

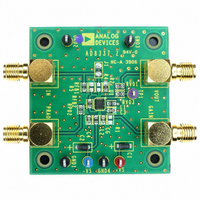

AD8337-EVALZ

Manufacturer Part Number

AD8337-EVALZ

Description

BOARD EVALUATION FOR AD8337

Manufacturer

Analog Devices Inc

Series

X-AMP®r

Specifications of AD8337-EVALZ

Channels Per Ic

1 - Single

Amplifier Type

Voltage Feedback

Output Type

Single-Ended

Slew Rate

625 V/µs

-3db Bandwidth

280MHz

Operating Temperature

-40°C ~ 85°C

Current - Supply (main Ic)

18.5mA

Voltage - Supply, Single/dual (±)

±2.5 V ~ 5 V

Board Type

Fully Populated

Utilized Ic / Part

AD8337

Silicon Manufacturer

Analog Devices

Application Sub Type

Variable Gain Amplifier

Kit Application Type

Amplifier

Silicon Core Number

AD8337

Kit Contents

Board

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Current - Output / Channel

-

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

AD8337-EVALZ

Manufacturer:

Analog Devices Inc

Quantity:

135

AD8337

The offset voltage effect of the AD8337, as with all VGAs, can

appear as a complex waveform when observed across the range

of V

a unique offset voltage (V

swept through its voltage range. The offset voltage profile seen

in Figure 15 is a typical example. If the V

modulated, the output is the product of the V

profile of the offset voltage. This is observed on a scope as a

small ac signal, as shown in Figure 74. In Figure 74, the signal

applied to the V

signal is slightly less than 4 mV p-p.

The profile of the waveform shown in Figure 74 is consistent

over a wide range of signals from dc to about 20 kHz. Above

20 kHz, secondary artifacts can be generated due to the effects

of minor internal circuit tolerances, as shown in Figure 75.

These artifacts are caused by settling and time constants of the

interpolator circuit and appear at the output as the voltage

spikes, as shown in Figure 75.

GAIN

–10

–10

10

–2

–4

–6

–8

10

–2

–4

–6

–8

–800

–800

8

6

4

2

0

8

6

4

2

0

voltage. Generated by multiple sources, each device has

V

V

Figure 74. Offset Voltage vs. V

S

S

V

V

= ±2.5V

INPUT

OUTPUT

= ±2.5V

S

S

INPUT

OUTPUT

–600

–600

= 2.5

= 2.5

GAIN

Figure 75. V

input is a 1 kHz ramp, and the output voltage

–400

–400

OS

OS

–200

–200

) profile while the GAIN input is

Profile for a 50 kHz Ramp

V

V

GAIN

GAIN

SPIKE

0

0

(mV)

(mV)

GAIN

200

200

for a 1 kHz Ramp

GAIN

400

400

GAIN

input voltage is

SPIKE

and the dc

600

600

800

800

Rev. C | Page 22 of 32

Under certain circumstances, the product of V

offset profile plus spikes is a coherent spurious signal within the

signal band of interest and indistinguishable from desired

signals. In general, the slower the ramp applied to the GAIN

Pin, the smaller the spikes are. In most applications, these

effects are benign and not an issue.

THERMAL CONSIDERATIONS

The thermal performance of LFCSPs, such as the AD8337,

departs significantly from that of leaded devices such as the

larger TSSOP or QFSP. In larger packages, heat is conducted

away from the die by the path provided by the bond wires and

the device leads. In LFCSPs, the heat transfer mechanisms are

surface-to-air radiation from the top and side surfaces of the

package and conduction through the metal solder pad on the

mounting surface of the device.

θ

Heat transfer away from the die is a three-dimensional dynamic,

and the path is through the bond wires, leads, and the six

surfaces of the package. Because of the small size of LFCSPs, the

θ

thermodynamic rules.

The θ

tab is soldered to the board and that there are three additional

ground layers beneath the device connected by at least four vias.

For a device with an unsoldered pad, the θ

becoming 138°C/W.

PSI (Ψ)

Table 2 lists a subset of the classic theta specification, Ψ

junction to top). θ

the case, involving the six outside surfaces of the package. Ψ

is a subset of the theta value and the thermal gradient from the

junction (die) to each of the six surfaces. Ψ can be different for

each of the surfaces, but since the top of the package is a fraction of

a millimeter from the die, the surface temperature of the package is

very close to the die temperature. The die temperature is calculated

as the product of the power dissipation and Ψ

surface temperature and power dissipation are easily measured, it

follows that the die temperature is easily calculated. For example,

for a dissipation of 180 mW and a Ψ

temperature is slightly less than 1°C higher than the surface

temperature.

BOARD LAYOUT

Because the AD8337 is a high frequency device, board layout is

critical. It is very important to have a good ground plane

connection to the VCOM pin. Coupling through the ground

plane, from the output to the input, can cause peaking at higher

frequencies.

JC

JC

is the traditional thermal metric used for integrated circuits.

is not measured conventionally. Instead, it is calculated using

JC

value of the AD8837 listed in Table 2 assumes that the

JC

is the metric of heat transfer from the die to

JT

of 5.3°C/W, the die

JC

nearly doubles,

JT

GAIN

. Since the top

and the

JT

(Psi

(XY)