KSZ8041NL-EVAL Micrel Inc, KSZ8041NL-EVAL Datasheet - Page 19

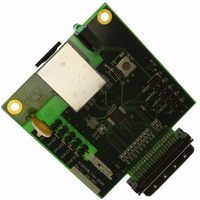

KSZ8041NL-EVAL

Manufacturer Part Number

KSZ8041NL-EVAL

Description

BOARD EVALUATION FOR KSZ8041NL

Manufacturer

Micrel Inc

Specifications of KSZ8041NL-EVAL

Main Purpose

Interface, Ethernet PHY

Embedded

No

Utilized Ic / Part

KSZ8041NL

Primary Attributes

Single Chip PHY, 10BASE-T/100BASE-TX

Secondary Attributes

MII, RMII, HP Auto MDI, MDI-X Auto Polarity Correction

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

576-1621

Micrel, Inc.

Strapping Options – KSZ8041RNL

Note:

1.

Pin strap-ins are latched during power-up or reset. In some systems, the MAC receive input pins may drive high during

power-up or reset, and consequently cause the PHY strap-in pins on the RMII signals to be latched high. In this case, it is

recommended to add 1K pull-downs on these PHY strap-in pins to ensure the PHY does not strap-in to ISOLATE mode,

or is not configured with an incorrect PHY Address.

September 2010

Pin Number

15

14

13

18

29

28

20

31

16

30

Ipu/O = Input with internal pull-up (40K +/-30%) during power-up/reset; output pin otherwise.

Ipd/O = Input with internal pull-down (40K +/-30%) during power-up/reset; output pin otherwise.

Pin Name

PHYAD2

PHYAD1

PHYAD0

CONFIG2

CONFIG1

CONFIG0

ISO

SPEED

DUPLEX

NWAYEN

Type

Ipd/O

Ipd/O

Ipu/O

Ipd/O

Ipd/O

Ipd/O

Ipd/O

Ipu/O

Ipu/O

Ipu/O

(1)

Pin Function

The PHY Address is latched at power-up / reset and is configurable to any value from

1 to 7.

The default PHY Address is 00001.

PHY Address bits [4:3] are always set to ‘00’.

The CONFIG[2:0] strap-in pins are latched at power-up / reset and are defined as

follows:

ISOLATE mode

During power-up / reset, this pin value is latched into register 0h bit 10.

SPEED mode

During power-up / reset, this pin value is latched into register 0h bit 13 as the Speed

Select, and also is latched into register 4h (Auto-Negotiation Advertisement) as the

Speed capability support.

DUPLEX mode

During power-up / reset, this pin value is latched into register 0h bit 8 as the Duplex

Mode.

Nway Auto-Negotiation Enable

During power-up / reset, this pin value is latched into register 0h bit 12.

CONFIG[2:0]

000

001

010

011

100

101

110

111

Pull-up = Enable

Pull-down (default) = Disable

Pull-up (default) = 100Mbps

Pull-down = 10Mbps

Pull-up (default) = Half Duplex

Pull-down = Full Duplex

Pull-up (default) = Enable Auto-Negotiation

Pull-down = Disable Auto-Negotiation

Mode

Reserved – not used

RMII

Reserved – not used

Reserved – not used

Reserved – not used

Reserved – not used

Reserved – not used

Reserved – not used

19

M9999-090910-1.4

KSZ8041NL/RNL