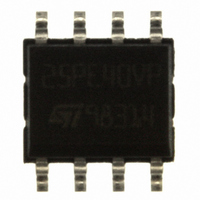

M25PE40-VMN6TP NUMONYX, M25PE40-VMN6TP Datasheet - Page 42

M25PE40-VMN6TP

Manufacturer Part Number

M25PE40-VMN6TP

Description

IC FLASH 4MBIT 75MHZ 8SOIC

Manufacturer

NUMONYX

Series

Forté™r

Datasheet

1.M25PE40-VMN6TP.pdf

(62 pages)

Specifications of M25PE40-VMN6TP

Format - Memory

FLASH

Memory Type

FLASH

Memory Size

4M (512K x 8)

Speed

75MHz

Interface

SPI, 3-Wire Serial

Voltage - Supply

2.7 V ~ 3.6 V

Operating Temperature

-40°C ~ 85°C

Package / Case

8-SOIC (3.9mm Width)

Cell Type

NOR

Density

4Mb

Access Time (max)

15ns

Interface Type

Serial (SPI)

Address Bus

1b

Operating Supply Voltage (typ)

3.3V

Operating Temp Range

-40C to 85C

Package Type

SOIC N

Sync/async

Synchronous

Operating Temperature Classification

Industrial

Operating Supply Voltage (min)

2.7V

Operating Supply Voltage (max)

3.6V

Word Size

8b

Number Of Words

512K

Supply Current

8mA

Mounting

Surface Mount

Pin Count

8

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

M25PE40-VMN6TPTR

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

M25PE40-VMN6TP

Manufacturer:

ST

Quantity:

20 000

Part Number:

M25PE40-VMN6TPBA

Manufacturer:

MICRON

Quantity:

20 000

Power-up and power-down

7

42/62

Power-up and power-down

At power-up and power-down, the device must not be selected (that is Chip Select (S) must

follow the voltage applied on V

A safe configuration is provided in

To avoid data corruption and inadvertent write operations during power-up, a Power On

Reset (POR) circuit is included. The logic inside the device is held reset while V

than the Power On Reset (POR) threshold voltage, V

the device does not respond to any instruction.

Moreover, the device ignores all Write Enable (WREN), Page Write (PW), Page Program

(PP), Page Erase (PE) and Sector Erase (SE) instructions until a time delay of t

elapsed after the moment that V

operation of the device is not guaranteed if, by this time, V

Write, Program or Erase instructions should be sent until the later of:

These values are specified in

If the delay, t

selected for READ instructions even if the t

As an extra protection, the Reset (Reset) signal could be driven Low for the whole duration

of the power-up and power-down phases.

At power-up, the device is in the following state:

Normal precautions must be taken for supply rail decoupling, to stabilize the V

Each device in a system should have the V

the package pins. (Generally, this capacitor is of the order of 100 nF).

At power-down, when V

(POR) threshold voltage, V

to any instruction. (The designer needs to be aware that if a Power-down occurs while a

Write, Program or Erase cycle is in progress, some data corruption can result.)

V

V

t

t

The device is in the Standby Power mode (not the Deep Power-down mode)

The Write Enable Latch (WEL) bit is reset

The Write In Progress (WIP) bit is reset

The Lock Registers are reset (Write Lock bit, Lock Down bit) = (0, 0).

PUW

VSL

CC

SS

(min) at power-up, and then for a further delay of t

at power-down.

after V

after V

VSL

, has elapsed, after V

CC

CC

passed the V

passed the V

CC

WI

drops from the operating voltage, to below the Power On Reset

, all operations are disabled and the device does not respond

Table

CC

CC

CC

) until V

WI

Section 3: SPI

(min) level.

rises above the V

11.

threshold

CC

has risen above V

CC

CC

PUW

reaches the correct value:

rail decoupled by a suitable capacitor close to

delay is not yet fully elapsed.

modes.

WI

WI

– all operations are disabled, and

threshold. However, the correct

CC

VSL

CC

is still below V

(min), the device can be

CC

CC

(min). No

PUW

CC

supply.

M25PE40

is less

has