MT46H64M16LFCK-5 IT:A TR Micron Technology Inc, MT46H64M16LFCK-5 IT:A TR Datasheet - Page 45

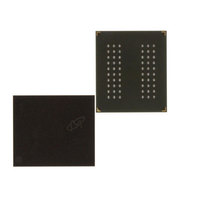

MT46H64M16LFCK-5 IT:A TR

Manufacturer Part Number

MT46H64M16LFCK-5 IT:A TR

Description

IC DDR SDRAM 1GBIT 60VFBGA

Manufacturer

Micron Technology Inc

Datasheet

1.MT46H64M16LFCK-5A_TR.pdf

(95 pages)

Specifications of MT46H64M16LFCK-5 IT:A TR

Format - Memory

RAM

Memory Type

Mobile DDR SDRAM

Memory Size

1G (64M x 16)

Speed

200MHz

Interface

Parallel

Voltage - Supply

1.7 V ~ 1.95 V

Operating Temperature

-40°C ~ 85°C

Package / Case

60-VFBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Initialization

PDF: 09005aef82ce3074

1gb_ddr_mobile_sdram_t48m.pdf - Rev. K 07/09 EN

Prior to normal operation, the device must be powered up and initialized in a prede-

fined manner. Using initialization procedures other than those specified will result in

undefined operation.

If there is an interruption to the device power, the device must be re-initialized using

the initialization sequence described previously to ensure proper functionality of the

device.

To properly initialize the device, this sequence must be followed:

After steps 1–10 are completed, the device has been properly initialized and is ready to

receive any valid command.

10. Issue NOP or DESELECT commands for at least

1. The core power (V

2. When power supply voltages are stable and the CKE has been driven HIGH, it is

3. When the clock is stable, a 200μs minimum delay is required by the Mobile

4. Issue a PRECHARGE ALL command.

5. Issue NOP or DESELECT commands for at least

6. Issue an AUTO REFRESH command followed by NOP or DESELECT commands

7. Using the LOAD MODE REGISTER command, load the standard mode register as

8. Issue NOP or DESELECT commands for at least

9. Using the LOAD MODE REGISTER command, load the extended mode register to

It is recommended that V

must never exceed V

HIGH (see Figure 15 (page 46)). Alternatively, initialization can be completed

with CKE LOW provided that CKE transitions HIGH

(page 47)).

safe to apply the clock.

LPDDR prior to applying an executable command. During this time, NOP or DESE-

LECT commands must be issued on the command bus.

for at least

or DESELECT commands for at least

must be issued. Typically, both of these commands are issued at this stage as de-

scribed above.

desired.

the desired operating modes. Note that the sequence in which the standard and

extended mode registers are programmed is not critical.

t

RFC time. Issue a second AUTO REFRESH command followed by NOP

DD

DD

) and I/O power (V

. Standard initialization requires that CKE be asserted

45

DD

and V

1Gb: x16, x32 Mobile LPDDR SDRAM

Micron Technology, Inc. reserves the right to change products or specifications without notice.

DDQ

t

RFC time. Two AUTO REFRESH commands

be from the same power source, or V

DDQ

) must be brought up simultaneously.

t

t

t

RP time.

MRD time.

MRD time.

t

IS prior to T0 (see Figure 16

©2007 Micron Technology, Inc. All rights reserved.

Initialization

DDQ