CAT25160YI-GT3 ON Semiconductor, CAT25160YI-GT3 Datasheet - Page 8

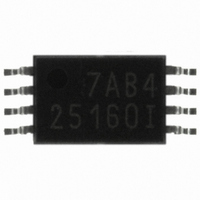

CAT25160YI-GT3

Manufacturer Part Number

CAT25160YI-GT3

Description

IC EEPROM 16KBIT 10MHZ 8TSSOP

Manufacturer

ON Semiconductor

Datasheet

1.CAT25080YI-GT3.pdf

(16 pages)

Specifications of CAT25160YI-GT3

Format - Memory

EEPROMs - Serial

Memory Type

EEPROM

Memory Size

16K (2K x 8)

Speed

10MHz

Interface

SPI, 3-Wire Serial

Voltage - Supply

1.8 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Package / Case

8-TSSOP

Density

16Kb

Interface Type

Serial (SPI)

Organization

2Kx8

Access Time (max)

75ns

Frequency (max)

5MHz

Write Protection

Yes

Data Retention

100Year

Operating Supply Voltage (typ)

2.5/3.3/5V

Package Type

TSSOP

Operating Temp Range

-40C to 85C

Supply Current

5mA

Operating Supply Voltage (min)

1.8V

Operating Supply Voltage (max)

5.5V

Operating Temperature Classification

Industrial

Mounting

Surface Mount

Pin Count

8

Maximum Clock Frequency

10 MHz

Access Time

40 ns

Supply Voltage (max)

5.5 V

Supply Voltage (min)

1.8 V

Maximum Operating Current

2 mA

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

Operating Supply Voltage

2.5 V, 3.3 V, 5 V

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

25160YI-GT3

CAT25160YI-GT3TR

CAT25160YI-GT3TR

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CAT25160YI-GT3

Manufacturer:

AMOSENSE

Quantity:

958

Part Number:

CAT25160YI-GT3

Manufacturer:

ON/安森美

Quantity:

20 000

Write Status Register

instruction according to timing shown in Figure 7. Only bits

2, 3 and 7 can be written using the WRSR command.

SCK

SO

CS

The Status Register is written by sending a WRSR

SI

Dashed Line = mode (1, 1)

SCK

WP

WP

CS

Dashed Line = mode (1, 1)

0

0

0

1

HIGH IMPEDANCE

0

2

0

3

OPCODE

0

4

0

5

Figure 7. WRSR Timing

Figure 8. WP Timing

0

http://onsemi.com

6

1

7

8

t

WPS

MSB

7

8

Write Protection

Block Protect bits BP0 and BP1 against being inadvertently

altered. When WP is low and the WPEN bit is set to “1”,

write operations to the Status Register are inhibited. WP

going low while CS is still low will interrupt a write to the

status register. If the internal write cycle has already been

initiated, WP going low will have no effect on any write

operation to the Status Register. The WP pin function is

blocked when the WPEN bit is set to “0”. The WP input

timing is shown in Figure 8.

The Write Protect (WP) pin can be used to protect the

t

9

6

WPH

10

5

11

4

DATA IN

12

3

13

2

14

1

15

0