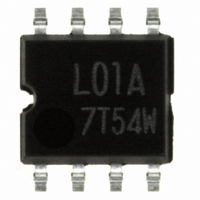

BR24L01AF-WE2 Rohm Semiconductor, BR24L01AF-WE2 Datasheet - Page 28

BR24L01AF-WE2

Manufacturer Part Number

BR24L01AF-WE2

Description

IC EEPROM 1KBIT 400KHZ 8SOP

Manufacturer

Rohm Semiconductor

Specifications of BR24L01AF-WE2

Memory Size

1K (128 x 8)

Format - Memory

EEPROMs - Serial

Memory Type

EEPROM

Speed

400kHz

Interface

I²C, 2-Wire Serial

Voltage - Supply

1.8 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Package / Case

8-SOP

Clock Frequency

400kHz

Supply Voltage Range

1.8V To 5.5V

Memory Case Style

SOP

No. Of Pins

8

Operating Temperature Range

-40°C To +85°C

Svhc

No SVHC (18-Jun-2010)

Package /

RoHS Compliant

Memory Configuration

128 X 8

Interface Type

I2C, Serial

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

BR24L01AF-WE2TR

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

BR24L01AF-WE2

Manufacturer:

ROHM Semiconductor

Quantity:

1 835

Company:

Part Number:

BR24L01AF-WE2

Manufacturer:

ROHM

Quantity:

21 523

Part Number:

BR24L01AF-WE2

Manufacturer:

ROHM/罗姆

Quantity:

20 000

●Write Command

© 2009 ROHM Co., Ltd. All rights reserved.

BR24L□□-W Series,BR24S□□□-W Series

www.rohm.com

○Write cycle

・Arbitrary data is written to EEPROM. When to write only 1 byte, byte write normally used, and when to write continuous

・Data is written to the address designated by word address (n-th address).

・By issuing stop bit after 8bit data input, write to memory cell inside starts.

・When internal write is started, command is not accepted for tWR (5ms at maximum).

・By page write cycle, the following can be written in bulk: Up to 16 bytes (BR24S08-W, BR24S16-W)

・As for page write command of BR24S08-W and, BR24S16-W, after page select bit(PS) of slave address is designated

・As for page write cycle of BR24S32-W and BR24S64-W , after the significant 7 bits (in the case of BR24S32-W) of word

・As for page write cycle of BR24S128-W and BR24S256-W, after the significant 9 bit (in the case of BR24S128-W) of word

Up to 64 arbitrary bytes can be written. (In the case of BR24S128/256-W)

data of 2 bytes or more, simultaneous write is possible by page write cycle. The maximum number of write bytes is

specified per device of each capacity.

And when data of the maximum bytes or higher is sent, data from the first byte is overwritten.

(Refer to "Internal address increment of "Notes on page write cycle" in P24/32.)

arbitrarily, by continuing data input of 2 bytes or more, the address of insignificant 4 bits is incremented internally, and data

up to 16 bytes can be written.

address, or the significant 8 bits (in the case of BR24S64-W) of word address are designated arbitrarily, by continuing data

input of 2 bytes or more, the address of insignificant 5 bits is incremented internally, and data up to 32 bytes can be written.

address, or the significant 10bit (in the case of BR24S256-W) of word address are designated arbitrarily, by continuing

data input of 64 bytes or more.

Fig.33 Byte write cycle (BR24S08/16-W)

Fig.34 Byte write cycle (BR24S32/64/128/256-W)

Fig.35 Page write cycle (BR24S08/16-W)

Fig.36 Page write cycle (BR24S32/64/128/256-W)

Note)

Fig.37 Difference of slave address each type

S D A

L IN E

SDA

LINE

SDA

LINE

S D A

L IN E

R

S

T

A

R

S

A

R

S

T

A

T

T

T

T

R

S

T

A

T

1 0

1

1

1 0

0

0

A D D R E S S

A D D R E S S

1

S L A V E

1

Note)

S L A V E

N o te )

1

1

ADDRESS

ADDRESS

0

Note)

SLAVE

Note)

SLAVE

0

注 )

A 2

0

0

1 0

A 2

A2

A2

A 1

A 1

A 0

A1

A1

A 0

W

W

R

T

E

R

I

/

A0

A0

A

C

K

W

1

R

W

W

R

R

/

W

W

R

/

R

E

/

W

T

E

T

R

T

E

I

I

I

*

C

A

K

W A

1 4

C

A

C

K

A D D R E S S (n )

0

A

K

W A

*1

1 st W O R D

W A

13

WA

*

7

*1 *2 *3

7

*1

A 2

W A

1 2

WA

14

1st WORD

ADDRESS

A D D R E S S (n )

W A

11

WA

13

A 1

W O R D

ADDRESS

WA

12

A 0

WORD

*1

WA

11

C

A

K

W A

0

WA

A D D R E S S (n )

0

2 n d W O R D

A

C

K

*1 In BR24S16-W, A2 becomes P2

*2 In BR24S08/16-W, A1 becomes P1

*3 In BR24S08/16-W, A0 becomes P0

A

C

K

A

C

K

D 7

D7

D A T A (n )

W A

2nd WORD

0

ADDRESS

DATA

A

C

K

D 7

D A T A (n )

D 0

D0

WA

A

C

K

: Up to 32 bytes (BR24S32-W, BR24S64-W)

: Up to 64 bytes (BR24S128-W, BR24S256-W)

0

28/40

A

C

K

C

A

K

D7

S

O

P

T

D 0

D A T A (n + 1 5 )

A

C

K

DATA

D A TA (n + 3 1 )

D 0

*2

A

C

K

D0

*2

D 0

S

O

P

T

A

C

K

A

C

K

S

O

P

T

O

S

T

P

*1 As for WA12, BR24S32-W becomes Don't care.

*1 As for WA12, BR24S32-W becomes Don't care.

*2 As for BR24S128/256-W becomes (n+63).

As for WA13, BR24S32/64-W becomes Don't care.

As for WA14, BR24S32/64/128-W becomes Don't care.

As for WA13, BR24S32/64-W becomes Don't care.

As for WA14, BR24S32/64/128-W becomes Don't care.

Technical Note

2009.09 - Rev.D