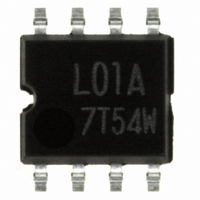

BR24L01AF-WE2 Rohm Semiconductor, BR24L01AF-WE2 Datasheet

BR24L01AF-WE2

Specifications of BR24L01AF-WE2

Available stocks

Related parts for BR24L01AF-WE2

BR24L01AF-WE2 Summary of contents

Page 1

TECHNICAL NOTE High Reliability Series Serial EEPROM Series BUS Serial EEPROMs BR24L□□-W Series BR24L01A-W, BR24L02-W, BR24L04-W, BR24L08-W, BR24L16-W, BR24L32-W, BR24L64-W BR24S□□□-W Series BR24S16-W, BR24S32-W, BR24S64-W, BR24S128-W, BR24S256-W ROHM's series of serial EEPROMs represent the highest level of ...

Page 2

I C BUS Serial EEPROMs BR24L□□-W Series BR24L01A-W, BR24L02-W, BR24L04-W, BR24L08-W, BR24L16-W, BR24L32-W, BR24L64-W ●Description BR24L□□-W series is a serial EEPROM of I ●Features ・ Completely conforming to the world standard I data(SDA) ・ Other devices than EEPROM can ...

Page 3

... FAST-MODE. When power source voltage goes down, action at high speed is not carried out, therefore, at Vcc=2.5V~5.5V , 400kHz, namely, action is made in FASTMODE. (Action is made also in STANDARD-MODE) Vcc=1.8V~2.5V is only action in 100kHz STANDARD-MODE. ●Memory cell characteristics (Ta=25℃, Vcc=1.8~5.5V) Unit Limits - ...

Page 4

SCL tSU:DAT tLOW tHD:STA SDA (入力) (input) tBUF tPD SDA (出力) (output) ○Input read at the rise edge of SCL ○Data output in sync with the fall of SCL Fig.1-(a) Sync ...

Page 5

Typ. ones SPEC 2 Ta=85℃ Ta=-40℃ Ta=25℃ Vcc[V] Fig.3 H input voltage VIH1,2 1 0.8 0.6 Ta=25℃ Ta=85℃ 0.4 SPEC 0.2 Ta=-40℃ ...

Page 6

Typ. ones). 50 SPEC1,2 0 Ta=-40℃ Ta=25℃ -50 Ta=85℃ -100 -150 -200 Vcc[V] Fig.21 Input data hold time tHD:DAT(HIGH) 300 SPEC2 200 SPEC1 100 Ta=85℃ 0 Ta=-40℃ -100 ...

Page 7

C BUS communication 2 ○I C BUS data communication BUS data communication starts by start condition input, and ends by stop condition input. Data is always 8bit long, and acknowledge is always required after each ...

Page 8

... Fig.39 Page write cycle (BR24L32/64-W) ・Data is written to the address designated by word address (n-th address) ・By issuing stop bit after 8bit data input, write to memory cell inside starts. ・When internal write is started, command is not accepted for tWR (5ms at maximum). ・By page write cycle, the following can be written in bulk : bytes ( BR24L01A-W, BR24L02-W) ...

Page 9

SLAVE WORD R T ADDRESS ADDRESS(n) SDA *1 LINE Note Fig.41 ...

Page 10

Command ○Read cycle Data of EEPROM is read. In read cycle, there are random read cycle and current read cycle. Random read cycle is a command to read data by designating address, and is used generally. Current read cycle ...

Page 11

Software reset is executed when to avoid malfunction after power on, and to reset during command input. Software reset has several kinds, and 3 kinds of them are shown in the figure below. (Refer to Fig.48(a), Fig.48(b), and ...

Page 12

WP is usually fixed to 'H' or 'L', but when WP is used to cancel write cycle and so forth, pay attention to the following WP valid timing. During write cycle execution, in cancel valid ...

Page 13

SDA terminal SDA is NMOS open drain, so requires pull up resistance. As for this resistance value (R value from microcontroller and larger the consumption current ...

Page 14

BUS recommended that SDA port is of open drain input/output. However, when to use CMOS input / output of tri state to SDA port, insert a series resistance Rs ...

Page 15

C BUS input / output circuit ○Input (A0,A2,SCL) Fig.57 Input pin circuit diagram ○Input / output (SDA) Fig.58 Input / output pin circuit diagram ○Input (A1, WP) Fig.59 Input pin circuit diagram ●Notes on power ON At power ...

Page 16

Set SDA and SCL so as not to become 'Hi-Z'. When the above conditions 1 and 2 cannot be observed, take the following countermeasures the case when the above condition 1 cannot be observed. When SDA becomes ...

Page 17

I C BUS Serial EEPROMs BR24S□□□-W Series BR24S16-W, BR24S32-W, BR24S64-W, BR24S128-W, BR24S256-W ●Description BR24S□□□-W series is a serial EEPROM of I ●Features ・ Completely conforming to the world standard I (SDA) ・ Other devices than EEPROM can be connected ...

Page 18

... SDA START BIT Fig.1-(b) Start - stop bit timing SCL SDA D0 ACK t WRITE DATA(n) WR STOP START CONDITION CONDITION Fig.1-(c) Write cycle timing ●Memory cell characteristics (Ta=25℃ Limits Unit - 0.3 ~ +6 450(SOP8) 450(SOP-J8) *2 Number of data rewrite 300(SSOP-B8) *3 330(TSSOP-B8 Data hold years ...

Page 19

11bit 12bit 13bit 14bit 15bit Adddress * decoder * Control circuit High voltage GND 4 generating circuit * 1 11bit: BR24S16-W 12bit: BR24S32-W 13bit: BR24S64-W 14bit: BR24S128-W 15bit: BR24S256-W ●Pin ...

Page 20

Typ. ones.) ●Characteristic data 2.5 SPEC 2 1.5 Ta=-40℃ Ta=25℃ 1 Ta=85℃ 0 SUPPLY VOLTAGE : Vcc[V] Fig.9 Current consumption at WRITE operation I (f =400kHz BR24S16/32/64-W) SCL ...

Page 21

Typ. ones.) ●Characteristic data 5 Ta=-40℃ 4 Ta=25℃ Ta=85℃ SPEC SUPPLY VOLTAGE : Vcc[V] Fig.24 BUS open time before transmission t BUF 0.6 Ta=-40℃ 0.5 Ta=25℃ ...

Page 22

C BUS communication 2 ○I C BUS data communication BUS data communication starts by start condition input, and ends by stop condition input. Data is always 8bit long, and acknowledge is always required after each ...

Page 23

... Fig.36 Page write cycle (BR24S32/64/128/256-W) ・Data is written to the address designated by word address (n-th address). ・By issuing stop bit after 8bit data input, write to memory cell inside starts. ・When internal write is started, command is not accepted for tWR (5ms at maximum). ・By page write cycle, the following can be written in bulk bytes (BR24S16-W) And when data of the maximum bytes or higher is sent, data from the first byte is overwritten. (Refer to " ...

Page 24

SLAVE WORD R T ADDRESS ADDRESS(n) SDA LINE Fig. ...

Page 25

Command ○Read cycle Data of EEPROM is read. In read cycle, there are random read cycle and current read cycle. Random read cycle is a command to read data by designating address, and is used generally. Current read cycle ...

Page 26

Software reset is executed when to avoid malfunction after power on, and to reset during command input. Software reset has several kinds, and 3 kids of them are shown in the figure below. (Refer to Fig.45(a), Fig.45(b), Fig.45(c).) ...

Page 27

WP is usually fixed to 'H' or 'L', but when WP is used to cancel write cycle and so forth, pay attention to the following WP valid timing. During write cycle execution, in cancel valid ...

Page 28

Pull up resistance of SDA terminal SDA is NMOS open drain, so requires pull up resistance. As for this resistance value (R from microcontroller and consumption ...

Page 29

Cautions on microcontroller connection ○ BUS recommended that SDA port is of open drain input/output. However, when to use CMOS input / output of tri state to SDA port, insert a series ...

Page 30

I C BUS input / output circuit ○ Input (A0, A1, A2, SCL, WP) Fig.54 Input pin circuit diagram ○ Input/Output (SDA) Fig.55 Input /output pin circuit diagram 30/32 ...

Page 31

Notes on power ON At power on internal circuit and set, Vcc rises through unstable low voltage area, and IC inside is not completely reset, and malfunction may occur. To prevent this, functions of POR circuit and ...

Page 32

Selection of order type BUS type Operating ROHM type 2 24 : I temperature C name L:-40℃~+85℃ S:-40℃~+85℃ ● Package specifications SOP8/SOP-J8/SSOP-B/TSSOP-B8/TSSOP-B8J 〈External appearance〉 SOP8 SOP-J8 5.0±0.2 4.9±0 ...

Page 33

Appendix No technical content pages of this document may be reproduced in any form or transmitted by any means without prior permission of ROHM CO.,LTD. The contents described herein are subject to change without notice. The specifications for the product ...