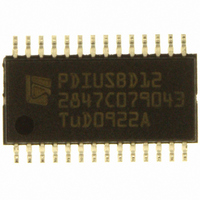

PDIUSBD12PWTM ST-Ericsson Inc, PDIUSBD12PWTM Datasheet - Page 22

PDIUSBD12PWTM

Manufacturer Part Number

PDIUSBD12PWTM

Description

IC USB INTRFC W/PARL BUS 28TSSOP

Manufacturer

ST-Ericsson Inc

Datasheet

1.PDIUSBD12PWTM.pdf

(40 pages)

Specifications of PDIUSBD12PWTM

Applications

USB Host/Peripheral Controller

Interface

Parallel

Voltage - Supply

3 V ~ 3.6 V, 4 V ~ 5.5 V

Package / Case

28-TSSOP

Mounting Type

Surface Mount

For Use With

D12 ISA PC EVAL KIT - EVAL KIT FOR PDIUSBD12 USB EPP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

568-1092-2

PDIUSBD12PW,118

PDIUSBD12PWDH-T

PDIUSBD12PW,118

PDIUSBD12PWDH-T

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

PDIUSBD12PWTM

Manufacturer:

ST

Quantity:

4 500

Philips Semiconductors

PDIUSBD12_9

Product data sheet

11.3.10 Acknowledge Setup

11.3.8 Validate Buffer

11.3.9 Set Endpoint Status

When a packet is completely received, an internal endpoint buffer full flag is set. All

subsequent packets will be refused by returning a NAK. When the microcontroller has

read data, it should free the buffer using the Clear Buffer command. When the buffer is

cleared, new packets will be accepted.

Code (Hex) — FA

Transaction — none

When the microprocessor has written data into an IN buffer, it should set the buffer full flag

using the Validate Buffer command. This indicates that data in the buffer is valid and can

be sent to the host when the next IN token is received.

Code (Hex) — 40 to 45

Transaction — write 1 B

A stalled control endpoint is automatically un-stalled when it receives a SETUP token,

regardless of the content of the packet. If the endpoint should stay in its stalled state, the

microcontroller can re-stall it.

When a stalled endpoint is un-stalled (either by the Set Endpoint Status command or by

receiving a SETUP token), it is also re-initialized. This flushes the buffer and if it is an OUT

buffer it waits for a DATA0 PID, if it is an IN buffer it writes a DATA0 PID.

Even when un-stalled, writing logic 0 to Set Endpoint Status initializes the endpoint.

Code (Hex) — F1

Transaction — none

The arrival of a SETUP packet flushes the IN buffer, and disables the Validate Buffer and

Clear Buffer commands for both IN and OUT endpoints.

The microcontroller needs to re-enable these commands using the Acknowledge Setup

command. This ensures that the last SETUP packet stays in the buffer and no packet can

be sent back to the host, until the microcontroller has acknowledged explicitly that it has

seen the SETUP packet.

Fig 14. Set Endpoint Status: bit allocation

STALLED: Logic 1 indicates the endpoint is stalled.

Rev. 09 — 11 May 2006

X X

7 6 5 4 3 2

X X

X X

X

1

USB peripheral controller with parallel bus

0

0

Power-on value

STALLED

reserved

004aaa806

© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

PDIUSBD12

21 of 39