CYP15G0101DXB-BBC Cypress Semiconductor Corp, CYP15G0101DXB-BBC Datasheet - Page 21

CYP15G0101DXB-BBC

Manufacturer Part Number

CYP15G0101DXB-BBC

Description

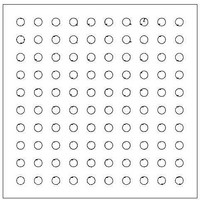

IC TXRX HOTLINK 100-LBGA

Manufacturer

Cypress Semiconductor Corp

Series

HOTlink II™r

Type

Transceiverr

Datasheet

1.CYP15G0101DXB-BBXC.pdf

(44 pages)

Specifications of CYP15G0101DXB-BBC

Package / Case

100-LBGA

Protocol

Fibre Channel

Voltage - Supply

3.135 V ~ 3.465 V

Mounting Type

Surface Mount

Product

PHY

Supply Voltage (min)

3.135 V

Supply Current

0.5 A

Maximum Operating Temperature

+ 70 C

Minimum Operating Temperature

0 C

Mounting Style

SMD/SMT

Number Of Channels

1

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

For Use With

CYP15G0101DX-EVAL - EVAL BRD FOR HOTLINK II

Number Of Drivers/receivers

-

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Contains lead / RoHS non-compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CYP15G0101DXB-BBC

Manufacturer:

DALLAS

Quantity:

2 601

Company:

Part Number:

CYP15G0101DXB-BBC

Manufacturer:

CYPRESS

Quantity:

200

Company:

Part Number:

CYP15G0101DXB-BBC

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

transmit and receive channels are disabled, and BIST is

disabled.

Following a device reset, it is necessary to enable the transmit

and receive channels for normal operation. This can be done by

sequencing the appropriate values on the BOE[1:0] inputs while

the OELE and RXLE signals are raised and lowered. For

systems that do not require dynamic control of power, or want

the part to power-up in a fixed configuration, it is also possible to

strap the RXLE and OELE control signals HIGH to permanently

enable their associated latches. Connection of the associated

BOE[1:0] signals to a stable HIGH will then enable the transmit

and receive channels as soon as the TRSTZ signal is

deasserted.

Output Bus

The receive channel presents a 12-signal output bus consisting

of

■

■

■

The bit assignments of the Data and Status are dependent on the

setting of DECMODE. This mapping is shown in

Table 13. Output Register Bit Assignments

When the 10B/8B decoder is bypassed (DECMODE = LOW),

the framed 10-bit character is presented to the receiver output

Document Number: 38-02031 Rev. *L

Note

24. The RXOP output is also driven from the Output Register, but its interpretation is under the separate control of PARCTL.

an eight-bit data bus

a three-bit status bus

a parity bit.

Signal Name

RXST[2]

RXD[7]

RXST[1]

RXST[0]

RXD[0]

RXD[1]

RXD[2]

RXD[3]

RXD[4]

RXD[5]

RXD[6]

(MSB)

(LSB)

DECMODE = LOW

COMDET

DOUT[0]

DOUT[1]

DOUT[2]

DOUT[3]

DOUT[4]

DOUT[5]

DOUT[6]

DOUT[7]

DOUT[8]

DOUT[9]

DECMODE = MID

[24]

or HIGH

RXST[2]

RXST[1]

RXST[0]

RXD[0]

RXD[1]

RXD[2]

RXD[3]

RXD[4]

RXD[5]

RXD[6]

RXD[7]

Table

13.

register, along with a status output (COMDET) indicating if the

character in the output register is one of the selected framing

characters. The bit usage and mapping of the external signals to

the raw 10B transmission character is shown in

Table 14. Decoder Bypass Mode (DECMODE = LOW)

The COMDET output is HIGH when the character in the output

register contains the selected framing character at the proper

character boundary, and LOW for all other bit combinations.

When the low-latency framer and half-rate receive port clocking

is also enabled (RFMODE = LOW, RXRATE = HIGH, and

RXCKSEL = MID), the framer will stretch the recovered clock to

the nearest 20-bit boundary such that the rising edge of RXCLK+

occurs when COMDET = HIGH in the output register.

When the Cypress or alternate-mode framer is enabled and

half-rate receive port clocking is also enabled (RFMODE LOW

and RXRATE = HIGH), the output clock is not modified when

framing is detected, but a single pipeline stage may be added or

subtracted from the data stream by the framer logic such that the

rising edge of RXCLK+ occurs when COMDET = HIGH in the

output register. This adjustment only occurs when the framer is

enabled (RFEN = HIGH). When the framer is disabled, the clock

boundaries are not adjusted, and COMDET may be asserted

during the rising edge of RXCLK– (if an odd number of

characters were received following the initial framing).

RXST[2]

Signal Name

RXD[7]

RXST[1]

RXST[0]

RXD[0]

RXD[1]

RXD[2]

RXD[3]

RXD[4]

RXD[5]

RXD[6]

(MSB)

(LSB)

Bus Weight

COMDET

2

2

2

2

2

2

2

2

2

2

0

1

2

3

4

5

6

7

8

9

CYW15G0101DXB

CYP15G0101DXB

CYV15G0101DXB

10B Name

Table

Page 21 of 44

a

b

d

e

g

h

c

i

f

j

14.

[+] Feedback